40納米500MHz DSP核心的時鐘設計與分析

時鐘串擾規避

在本文中,一直使用非默認時鐘網路規則來降低串擾影響。如下所示,選擇較高MET層進行時鐘網路布線:

rule layer preference Mn clock /sr70

rule layer preference Mn+1 clock /sr70

我們一直建議采用具有2倍寬和3倍間距的NDR(Non-default Rule)來降低耦和度。事實證實,這對PTSI有很大幫助。微捷碼工具中所定義的非默認規則。這種規則只應用于MET3及更高層,同樣還只應用于時鐘網絡中非葉級網路。

時鐘分析

時鐘分析是采用已開發的腳本,產生時鐘樹分布指標,*估時鐘樹的結果質量(QOR)。

RC分布擴展

RC延時分布是可用以改善設計期間時鐘樹魯棒性的第一個指標。時鐘樹RC延時百分比等于互連線延時在每個接收端(sink)總插入延時中所占比率。

對于每個時鐘網路:

%RC delay = [RC delay ]/[RC delay + Gate delay]

窄(10%)分布意味著良好的跨角點時鐘延時追蹤。互連線在時鐘路徑占主導地位與門在時鐘路徑占主導地位相交疊的機率比較小。這種分析不包括數據路徑時鐘樹。

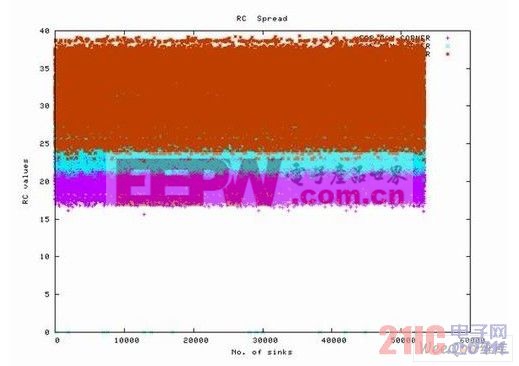

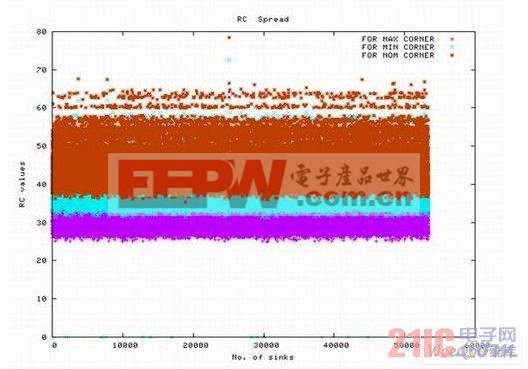

圖2顯示了一種更好的RC擴展分析 。在圖3中,采用了微捷碼自帶CTS的NOM角點RC擴展率在25%以上,而圖2的則在15%左右。在圖3中,MAX 角點RC擴展率在10%左右,而圖2的則在5%左右。

圖 2 使用新時鐘設計方法的RC擴展

圖3 使用微捷碼自帶CTS的RC擴展

評論