視頻監控系統中多畫面處理器的設計

字符疊加電路由NEC公司μPD6453組成。該芯片可在屏幕上顯示12行、每行24個字符、每個字符為12×18點陣。字符的大小、閃爍頻率可以根據需要進行調整,屏幕的背景色、字符的邊緣色以及字符本身的顏色也可以修改。該芯片內部除固化了191個日文、英文字母和數字等字符的字模以外,還固化了49個漢字(如年、月、日、時)的字模;另外該芯片提供16個字符的RAM空間,供用戶填入自定義字符。由于畫面處理器不需要疊加太多的不同字符,因而本設計不外加漢字字庫,這樣既節省了成本和線路板的空間,又簡化了電路結構。μPD6453所需的行、場同步信號及時鐘信號均由FPGA提供。單片機通過串行數據傳輸將一系列命令(包括所要顯示的字符或漢字、字符大小、字符的間距、字符的屬性)送往μPD6453,μPD6453收到命令后再將所要顯示的字符或漢字等信息送至FPGA。

2.8 視頻信號切換電路

該電路由MAX440組成。MAX440是一種內含寬帶視頻放大器的高速多路視頻選擇開關,可輸入8路視頻信號,輸出為1路視頻信號。在單片機的控制下,輸出可與8路視頻輸入中的任一路相連。該芯片的主要特點如下:

?帶寬為110MHz;微分增益為0.04%,微分相位為0.03度;

?開關切換時間為15ns,轉換速率為370V/μs;

?開/關時的輸入電容為4pF,無需外接補償元件。

2.9 報警信號的接收及處理

由單片機直接完成,無需經過FPGA。當有報警發生時,單片機收到報警信息,發出命令使蜂鳴器件發出警報聲,同時通知FPGA和μPD6453使對應的畫面閃爍并出現“報警”字樣。

3 FPGA器件XCS05XL的編程實現原理

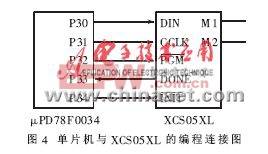

所謂編程就是利用單片機μPD78F0034將事先設計好的數據通過某種方式裝入XCS05XL中,以確定XCS05XL內部的CLB和IOB的功能以及布線通道的連接方式,數據的寫入只在編程過程中完成。在正常工作期間,存儲單元只用來提供固定的控制信號,編程存儲單元以陣列形式分布在XCS05XL中。每個CLB有幾百個編程數據位,每個編程數據位定義了一個靜態存儲單元的狀態,該存儲單元可以控制一個邏輯函數查找表位、一個數據選擇器輸入或一個互連開關晶體管。Xilinx開發系統可以將邏輯設計轉換成網絡表文件,它自動將邏輯電路分區、設置和布線,以PROM格式產生編程數據,并將數據存入PROM中。XCS05XL有三種編程模式:從串模式、主串模式和快速模式。編程開始前,芯片會自動檢測M1和M2腳以確定編程模式,編程結束后,這些腳就沒有用了。當M1和M2腳為高電平時,選從串模式,這也是目前最常用的一種編程模式。實際上,此時M1和M2腳可懸空。如果要選擇主串模式,則M1和M2腳必須與相連或通過1k℃的下拉電阻接地。

圖4所示為μPD78F0034單片機對FPGA器件XCSO5XL裝載編輯數據的示意圖。XCS05XL的編程模式選從串模式,因而其M1、M2腳懸空(即相當于接高電平)。XCS05XL的編輯數據存儲在單片機的FLASH ROM里,上電復位后,單片機通過P30腳將數據串行傳送到XCSO5XL中。XCS05XL所需的編程時鐘(CCLK)信號由單片機產生,在每個CCLK的上升沿,XCS05XL通過DIN腳接收輸入數據。

4 軟硬件設計時要注意的幾個問題

(1)使用幀存儲器AL422應注意的問題

?由于幀存儲器AL422是FIFO DRAM,因而須確保WCK和RCK信號始終有且信號的頻率不低于1MHz,因WCK和RCK中頻率較高者將作為DRAM的刷新時鐘信號。

?在AL422的/RRST信號的上升沿,/RE信號不能為低,這一點在確定FPGA的編程數據時要特點注意(因/RRST和/RE信號均由FPGA提供);

?AL422可在5V或3.3V電源電壓下工作,當使用5V電源時,其DEC腳(Pin19)須接2.2μF的去耦電容;當使用3.3V電源時,DEC腳(Pin19)可直接與3.3V相連,并通過0.1μF電容旁路到地;電容均使用鉭電容。由于使用3.3V時,器件功耗低,且受噪聲干擾小,因而在本設計中采用了3.3V電源對AL422供電。

(2)為避免視頻信號之間的串擾,各種模擬視頻信號間均用較粗的地線隔開,且視頻走線足夠寬。

以上介紹了黑白四畫面處理器的設計。為了節省線路板空間并使產品小巧玲瓏,所有的元器件及IC芯片均選用貼片式封裝。鑒于篇幅的限制,本文沒有討論多畫面處理器軟件方面的設計。至于9畫面和16畫面處理器的設計,其設計思想及組成方框圖與該4畫面處理器相類似,只不過要增加A/D、AL422及FPGA,軟件編程也復雜一些。

評論