視頻監(jiān)控系統(tǒng)中多畫(huà)面處理器的設(shè)計(jì)

2 各部分電路的結(jié)構(gòu)及工作原理

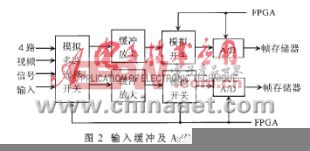

2.1 輸入緩沖及A/D轉(zhuǎn)換

該部分電路的主要功能是將輸入的模擬視頻信號(hào)轉(zhuǎn)換成數(shù)字視頻信號(hào)供FPGA器件處理,其方框圖如圖2所示。4路視頻信號(hào)經(jīng)過(guò)受FPGA控制的模擬多路選擇器后,輸出2路視頻信號(hào),經(jīng)過(guò)緩沖放大后送到受FPGA控制的模擬開(kāi)關(guān);然后再輸出給A/D,2路視頻信號(hào)需要2片A/D芯片。A/D芯片選TLC5510,該芯片是一種分辨率為8位、20MSPS(20兆采樣點(diǎn)/秒)的CMOS模/數(shù)轉(zhuǎn)換器。在FPGA的控制下,TLC5510將輸入的模擬視頻信號(hào)轉(zhuǎn)換成數(shù)字視頻誤,然后送往幀存儲(chǔ)器。

2.2 幀存儲(chǔ)器

幀存儲(chǔ)器選AVERLOGIC公司的AL422,共需要2片。AL422是存儲(chǔ)量為384KB×8Bits的FIFO(First In First Out)DRAM,它支持VGA、CCIR、NTSC、PAL和HDTV分辨率,具有獨(dú)立的讀/寫(xiě)操作及輸出使能控制;存儲(chǔ)時(shí)間為15ns的高速異步串行存取,可在5V或3.3V電源電壓下工作,標(biāo)準(zhǔn)的28腳SOP封裝。

2.3 FPGA器件

FPGA是本設(shè)計(jì)的核心,與傳統(tǒng)邏輯電路和門(mén)陣列相比具有不同的結(jié)構(gòu)。FPGA利用小型查找表(16×1RAM)來(lái)實(shí)現(xiàn)組合邏輯,每個(gè)查找表連接到一個(gè)D觸發(fā)器的輸入端,D觸發(fā)器再來(lái)驅(qū)動(dòng)其它邏輯或驅(qū)I/O。這些模塊利用金屬連線互相連接或連接到I/O模塊。FPGA通過(guò)向內(nèi)部靜態(tài)存儲(chǔ)單元加載編程數(shù)據(jù)來(lái)實(shí)現(xiàn)其FPGA通過(guò)向內(nèi)部靜態(tài)存儲(chǔ)單元加載編程數(shù)據(jù)來(lái)實(shí)現(xiàn)其邏輯,存儲(chǔ)在存儲(chǔ)單元中值決定了FPGA實(shí)現(xiàn)的功能;FPGA的這種結(jié)構(gòu)允許無(wú)限次的重新編程。由此可見(jiàn),用FPGA設(shè)計(jì)的產(chǎn)品調(diào)試修改及升級(jí)均很容易,且具有很大的靈活性。目前FPGA的種類(lèi)很多,在本設(shè)計(jì)中選用Spartan系列的XCS05XL。該芯片是Xilinx公司推出的低價(jià)格、高性能的FPGA,其主要特點(diǎn)如下:

?系統(tǒng)門(mén)的數(shù)目達(dá)到了5000,Logic cell數(shù)目達(dá)到了238,系統(tǒng)資源豐富;

?具備片上可編程分布式RAM,最多可編程的RAM達(dá)3200bit;

?分布式算術(shù)邏輯單元,支持分布式DSP運(yùn)算;

?靈活的高速時(shí)鐘網(wǎng)絡(luò),內(nèi)部三態(tài)總線;工作電壓為3.3V。

有關(guān)XCS05XL的詳細(xì)資料請(qǐng)參閱參考文獻(xiàn)[1]。

FPGA的編程數(shù)據(jù)存儲(chǔ)在單片機(jī)的FLASH ROM里。每次上電后單片機(jī)將編程數(shù)據(jù)裝入XCS05XL,編程模式選從串模式,因而其22腳(M1)和24腳(M0)懸空。編程數(shù)據(jù)裝入后,XCS05XL的邏輯功能就確定了;XCS05XL控制視頻信號(hào)的輸入及A/D轉(zhuǎn)換,在其內(nèi)部將每路視頻信號(hào)壓縮為原來(lái)的1/2,同時(shí)在單片機(jī)的控制下給每路疊加時(shí)間、日期、通道數(shù)字字符信息,然后將壓縮的四路視頻信號(hào)合成為一路完整的數(shù)字視頻信號(hào),并輸出給D/A,形成四分割輸出。

2.4 D/A轉(zhuǎn)換及輸出緩沖放大

D/A轉(zhuǎn)換電路將FPGA輸出的數(shù)字視頻信號(hào)轉(zhuǎn)移成模擬視頻信號(hào),然后經(jīng)過(guò)緩沖放大輸出給監(jiān)視器,D/A芯片選HI1171。該芯片是一種分辨率為8位,頻率為40MHz的高速D/A轉(zhuǎn)換器,其最大積分和微分線性誤差分別為1.3LSB和0.25LSB;最小建立時(shí)間僅為5ns,在單5V下工作,功耗只有80mW。輸出緩沖放大由分立元件組成。

評(píng)論