基于Fution模數混合FPGA芯片的心電儀片上系統開發

2.2 控制核心Core8051模塊設計

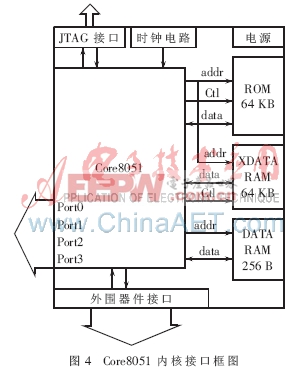

FPGA內部可以嵌入高速的Core8051處理器內核,它是整個系統的核心,負責有序地調用其余各功能模塊,同時又兼有數據處理任務,負責將ADC傳來的數據轉換成VGA可以顯示的數據。Core8051的硬件配置非常靈活,時鐘速度可以達到33 MHz,ROM的大小可以根據需要靈活地設置,該設計配置為64 KB。片內DATA RAM僅需256 B即可完成驅動VGA的功能,也可以擴展外部64 KB RAM,從而完成更強大的軟件功能。系統中設置單片機的片內DATA RAM為256 B,并通過系統總線擴展了外部64 KB的SRAM,系統框圖如圖4所示。

2.3 彩色顯示驅動模塊

比較成熟的TFT_LCD顯示驅動的開發大多數基于ARM[2-3]、DSP[4]的平臺。然而本系統使用的處理器是Coer8051,所以沒有辦法移植原有的驅動模塊。又因為圖像數據比較大,對處理器運算能力的要求比較高,所以結合Core8051和FPGA的特點重新設計了一種算法,降低需要處理的數據量,從而在Core8051的能力范圍內來完成心電圖像信息的顯示。

為了顯示一幅完整的圖像,按照液晶掃描的時鐘順序將事先準備好的一幀圖像數據逐次地輸入到數據端口,從而完成一幀圖像的顯示。由于要顯示的圖像只有心電信號是動態變化的,而其他的都是相對靜止不動的,也就是每一次掃描時數據信息是不變化的,整幅的圖像被分成動態的(心電圖像)和靜態的(背景、標度)兩部分。動態的由Core8051產生,并在特定時刻輸入到TFT_LCD;靜態的圖像信息事先存儲到FPGA中的存儲器中,每掃描一次都按照特定的順序輸入到LCD。通過這種方法,Core805就只需處理心電信號的信息,從而大大地減少了圖像數據的處理量,并完成圖像的顯示。該模塊的設計完成了低端處理器很難完成的實時彩色界面的驅動,即僅使用帶有256 B RAM的Core8051就可以顯示256色界面。

根據上述設想,可將液晶屏分成動態部分和靜態部分,如圖5所示。

圖5中除了“心電信號動態顯示區”中顯示出動態的心電圖像,其他部分包括“動態顯示區”中的背景圖像信息全部事先存儲在FPGA內部的Flash存儲器中。

動態顯示區可以用兩組數據來標注,設為:x0,y0,x1,y1,則這個動態顯示區每個定點的坐標就可以表示為(x0,y0)(x0,y1)(x1,y0)(x1,y1)。如圖5所示, 橫坐標表示時間t/s,縱坐標表示心電信號的幅值大小U/v,(x0,y0)處為(0,0)坐標點。在Core8051的基礎上設計編碼算法,對采集到的心電信號進行編碼,然后將心電信號轉換成顯示屏的坐標信號,然后根據坐標信號計算出心電圖像的數據,并在掃描時鐘的控制下逐次將數據按照順序輸入到LCD中, 這樣即可實現動態的心電圖像的顯示。

評論