基于Fution模數(shù)混合FPGA芯片的心電儀片上系統(tǒng)開發(fā)

Fution系列的FPGA是世界上首個(gè)基于Flash構(gòu)架的模數(shù)混合的FPGA,即在數(shù)字FPGA的基礎(chǔ)上加入了模擬電路部分,解決了傳統(tǒng)模擬電路和FPGA分離給設(shè)計(jì)帶來(lái)的諸多問(wèn)題,降低了PCB板的制作難度,縮小了產(chǎn)品的體積。FPGA的可編程性使得系統(tǒng)易于升級(jí)。同時(shí)在數(shù)字系統(tǒng)中引入模擬電路,簡(jiǎn)化了系統(tǒng)電路設(shè)計(jì)。

1 Fution FPGA介紹

Fution FPGA的主要特點(diǎn)主要體現(xiàn)在:

(1)單芯片:無(wú)需配置芯片;

(2)高安全性:晶體管受7層金屬保護(hù),具有AES和Flash Lock加密技術(shù);

(3)高可靠性:對(duì)高能量粒子轟擊具有免疫作用,具有很強(qiáng)的固件錯(cuò)誤免疫功能;

(4)上電即行:上電時(shí)間非常短,一般只有幾十個(gè)微秒左右;

(5)低功耗:無(wú)論是動(dòng)態(tài)功耗還是靜功耗都低于競(jìng)爭(zhēng)對(duì)手,IGLOO最低可達(dá)5 ?滋W;

(6)低系統(tǒng)成本:無(wú)需配置芯片,小功率電源芯片,無(wú)需加密芯片,PCB面積更小。

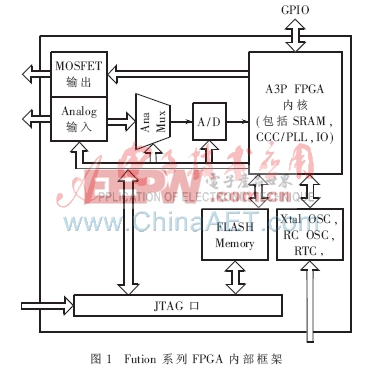

Fusion系列FPGA內(nèi)部框架如圖1所示。

2 片上系統(tǒng)的實(shí)現(xiàn)原理

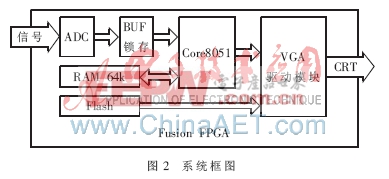

具體片上系統(tǒng)框圖如圖2所示。經(jīng)過(guò)心電信號(hào)采集傳感器采集的心電信號(hào)接入12位ADC,ADC將心電模擬信號(hào)轉(zhuǎn)換成數(shù)字信號(hào)被BUF鎖存,然后送給Core8051供其采集處理。Core8051中設(shè)計(jì)算法,將ADC傳來(lái)的數(shù)據(jù)轉(zhuǎn)換成VGA可以顯示的數(shù)據(jù),然后送給VGA驅(qū)動(dòng)模塊。

2.1 ADC模塊設(shè)計(jì)

Fution FPGA內(nèi)含采樣精度和轉(zhuǎn)換時(shí)間可以靈活配置的AD轉(zhuǎn)換器,為靈活的AD轉(zhuǎn)換方案提供了可能性。作為一種逐次逼近型ADC,這種轉(zhuǎn)換器具有高達(dá)600 Ks/s采樣率,器件內(nèi)部具有2.56 V的參考源,誤差在12位模式下為±6 LSB,具有自動(dòng)校準(zhǔn)功能。

利用FPGA內(nèi)部邏輯單元對(duì)ADC進(jìn)行配置:設(shè)置ADC精度為12位,參考電壓采用幅值為2.56 V精度為1%片內(nèi)電壓源供電,同時(shí)FPGA內(nèi)部的ADC具有Prescaler(預(yù)處理器),所以可以靈活地設(shè)置采樣電壓的范圍,更進(jìn)一步保證了AD轉(zhuǎn)換的精確度。ADC初始化工作過(guò)程如下:

(1)等待ADCRESET管腳釋放無(wú)效;

(2)ADCRESET管腳釋放無(wú)效后,ADC上電自校準(zhǔn);

(3)上電校準(zhǔn)后(CALIBRATE=1),對(duì)ACM 進(jìn)行配置;

(4)配置完成后,通過(guò)ADC_START來(lái)使ADC工作。

FPGA內(nèi)部邏輯單元進(jìn)行ADC的配置和初始化工作,從而控制ADC采樣,具體過(guò)程如圖3所示。

評(píng)論