基于ADPCM語音編解碼VLSI芯片的設計方法

input CLK, RECORD,PLAY;本文引用地址:http://www.104case.com/article/165873.htm

output CLK8K;

wire[3:0] code_in,code_out;

wire en_encoder,en_decoder,re_rst,pl_rst,WE,CS,CLK_8K;

wire [ADDR_WIDTH-1:0] ADDRESS;

assign CLK8K =CLK_8K;

CLOCK_GE U0 (CLK,RECORD, CLK_8K);

encoder_new U1 ( PCM_IN,re_rst ,en_encoder, CLK_8K ,code_in );

RAM U2 (ADDRESS,WE,CS,CLK_8K,code_in,code_out);

decoder_new U3 (pl_rst, CLK_8K ,code_out ,en_decoder,PCM_OUT);

controllogic U4(CS,re_rst,pl_rst,en_encoder,en_decoder,WE,ADDRESS,RECORD,PLAY,CLK_8K);

endmodule

子模塊電路設計及仿真

整個語音編解碼VLSI芯片包括編碼電路、解碼電路、存儲電路、控制電路和時鐘電路幾個部分。下面分別具體描述關鍵電路的設計。

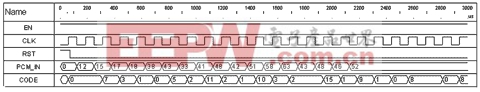

1 編碼電路

編碼電路實現數據壓縮功能,將輸入的PCM信號轉換成均勻的PCM碼,然后與預測信號進行差分,得到的差分信號經過“自適應量化器”進行壓縮編碼得到ADPCM碼,ADPCM碼被返回經過“逆自適應量化器”以及“自適應預測器”用來構建下一個預測信號。編碼電路仿真波形如圖3所示,其中PCM_IN為編碼器輸入信號(PCM碼),CODE為編碼后得到的輸出信號(ADPCM碼)。

圖3 編碼電路仿真波形

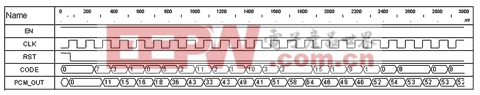

2 解碼電路

解碼電路實現解壓縮功能,將ADPCM碼經過“逆自適應量化器”得到量化差分信號,量化差分信號與預測值相加得到重構信號,然后轉換成PCM碼。解碼電路仿真波形如圖4所示,其中CODE為解碼器輸入信號(ADPCM碼),PCM_OUT為解碼后得到的輸出信號(PCM碼)。與圖3中編解碼前的PCM_IN對比,可以看出解碼誤差很小。

3 其他模塊

控制電路控制其他電路模塊的協調工作,在編碼的同時使能存儲器寫入信號,使編碼電路輸出數據可以及時存入存儲器;在解碼的同時使能存儲器讀出信號,編碼和解碼不能同時進行。時鐘電路主要實現對外部晶振的原始時鐘信號進行分頻,以得到電路系統實際所需的時鐘信號。本系統采用的外部晶振固有頻率為14.318MHz,經過分頻后可以獲得8kHz時鐘。存儲電路在控制電路的作用下,保存編碼所得的ADPCM碼(32kb/s),由于只需驗證電路的功能,所以只設定了2s的錄音存儲空間,即64kb存儲容量。

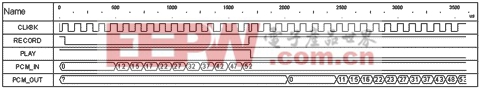

整體電路仿真

[table][/table] 在子模塊電路仿真正確后,對系統整體進行仿真,可以得到圖5所示波形。此次仿真輸入信號PCM_IN激勵采用Testbench產生。在編碼使能信號RECORD為“0”時,開始編碼,RECORD跳變到“1”時,編碼被屏蔽;此時解碼使能信號PLAY為“0”,開始解碼,PLAY跳變到“1”時,解碼被屏蔽。從圖中可以看出編碼前輸入信號PCM_IN的激勵和解碼后輸出PCM_OUT的響應基本符合。由于ADPCM算法本身是有損壓縮,可以確定本電路系統的設計是正確可靠的。

FPGA驗證及結論

本文基于FPGA驗證所設計的電路。這里選用Altera公司Cyclone系列的EP1C6Q240C8器件,其內部有90kb的存儲容量,6k個邏輯單元,2 個PLL。由于電路采用8kHz采樣頻率,編碼后的ADPCM碼為4位,設定錄音時間為2s,所以需要64kb存儲容量;同時,設計需要大約400個左右的邏輯單元。所以選用此低成本的FPGA即可滿足設計要求,而且基本上充分利用了內部資源。此芯片的引腳有240 個,能滿足外面的引腳連接,而且價格也易于接受。

FPGA驗證表明:電路的最大時鐘延遲為26.903ns,最高工作頻率可達37.17MHz,可以很好地再現被錄入的語音,具有較高的保真度和很好的實時性。在電子地圖、車載信息終端語音播報、治安報警系統,特別是便攜式語音記錄裝置等方面具有較高的應用價值。同時,也指明了數字語音壓縮處理高效設計方法的方向。

圖4 編碼電路仿真波形

圖5 系統仿真波形

評論