基于ADPCM語音編解碼VLSI芯片的設計方法

ADPCM(Adaptive Differential Pulse Code Modulation,自適應差分脈沖編碼調制)綜合了APCM的自適應特性和DPCM系統的差分特性,是一種性能較好的波形編碼。它的核心思想是:利用自適應改變量化階的大小,即使用小的量化階去編碼小的差值,使用大的量化階去編碼大的差值;使用過去的樣本值估算下一個輸入樣本的預測值,使實際樣本值和預測值之間的差值總是最小。ADPCM記錄的量化值不是每個采樣點的幅值,而是該點的幅值與前一個采樣點幅值之差。

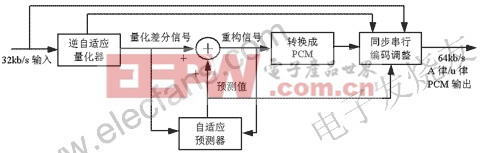

ADPCM是利用樣本與樣本之間的高度相關性和量化階自適應來壓縮數據的一種波形編碼技術。ADPCM標準是一個代碼轉換系統,它使用ADPCM轉換技術實現64kb/s A律或u律PCM(脈沖編碼調制)速率和32kb/s速率之間的相互轉換。ADPCM的簡化框圖如圖1所示。

ADPCM編解碼器的輸入信號是G.711 PCM代碼,采樣率是8kHz,每個代碼用8位表示,因此它的數據率為64kb/s。而ADPCM的輸出代碼是“自適應量化器”的輸出,該輸出是用4位表示的差分信號,它的采樣率仍然是8kHz,它的數據率為32kb/s,這樣就獲得了2∶1的數據壓縮。

電路的整體結構

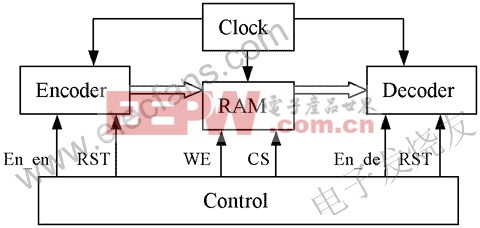

基于ADPCM算法,可將語音編解碼VLSI芯片分成編碼、解碼、存儲、控制和時鐘幾個模塊。編碼模塊實現數據壓縮功能,將輸入的PCM信號轉換成ADPCM碼;存儲模塊在控制模塊的作用下,保存編碼所得的ADPCM碼;解碼模塊實現解壓縮功能,將ADPCM碼轉換得到PCM碼;控制模塊的作用是控制其他模塊的協調工作;時鐘模塊主要實現對外部晶振的原始時鐘信號進行分頻,以得到電路系統實際所需的時鐘信號。

電路整體結構如圖2所示,其中En_en、En_de分別是編碼和解碼的使能信號,RST則為復位信號。當WE為“1”時,RAM寫有效,而當 WE為“0”時,RAM讀有效,CS為“1”時,RAM可進行寫或者讀操作。

(a) ADPCM編碼器

(b)ADPCM解碼器

圖1 ADPCM簡化框圖

電路設計過程

本文采用Top-down方法進行電路設計。主要設計流程如下:首先基于Verilog HDL運用Active-HDL進行電路的RTL級描述和功能仿真;將經過功能仿真正確的程序在Quartus II開發系統中進行綜合和適配;接下來將得到的網表文件(.vo)和具有時延信息的反標文件(.sdo)調入ModelSim SE中,并加入所選器件相應的器件庫進行時序仿真;時序仿真通過后,將Quartus II得到的“*.sof”文件通過JTAG配置模式下載到FPGA中進行不可掉電的實際測試,也可將“*.pof”文件通過AS配置模式下載到FPGA中進行可掉電的實際測試。電路系統的頂層程序如下。

圖2 電路整體結構圖

module ADPCM_TOP ( PCM_OUT,PCM_IN ,RECORD,PLAY,CLK, CLK8K);

parameter ADDR_WIDTH=14;

parameter PCM_WIDTH=8;

input [PCM_WIDTH-1:0] PCM_IN ;

wire [PCM_WIDTH-1:0] PCM_IN ;

output [PCM_WIDTH-1:0] PCM_OUT ;

wire [PCM_WIDTH-1:0] PCM_OUT ;

評論