雙口RAM芯片CY7C028的INS/GPS組合導(dǎo)航系統(tǒng)

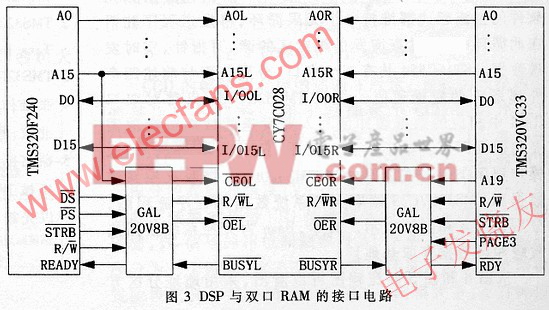

在組合導(dǎo)航系統(tǒng)中,CY7C028與兩個(gè)DSP芯片TMS320VC33和TMS320F240之間的接口電路如圖3所示。TMS320VC33的數(shù)據(jù)線寬度為32位,而CY7C028的數(shù)據(jù)位寬為16位,因此采用將TMS320VC33數(shù)據(jù)總線的低16位與雙口RAM的數(shù)據(jù)總線相連。TMS320VC33在發(fā)送32位的數(shù)據(jù)至又口RAM時(shí),分兩次完成,先寫低16位,再寫高16位。從雙口RAM讀取數(shù)據(jù)操作與發(fā)送類似。如前所述,使用雙口RAM的關(guān)鍵是解決左右端口同時(shí)操作同一RAM單元的競爭問題。圖3中采用了硬件判優(yōu)的方法,即將左右端口的BUSY信號(hào)經(jīng)相應(yīng)處理后分別引至支持插入等待時(shí)序的TMS320VC33和TMS320F240的對(duì)應(yīng)引腳,以解決左右端口對(duì)同一單元的爭用問題。

為了使整個(gè)系統(tǒng)成為完全可編程系統(tǒng),增加系統(tǒng)的靈活性,系統(tǒng)中邏輯控制選用可編程的邏輯器件GAL實(shí)現(xiàn),GAL選用Lattice公司的GAL20V8B芯片,并采用Lattice公司提供的ispDesignEXPERT集成開發(fā)軟件對(duì)其進(jìn)行邏輯編程。IspDesignEXPERT支持多種硬件編程語言,系統(tǒng)中采用ABEL語言進(jìn)行編程。左、右兩端GAL的輸入管腳信號(hào)定義如圖3中所示。

左端譯碼電路的邏輯方程為:

CE0L=DSA15#PS A15;

R/WL=R/WSTRB;

OEL=R/W STRB;

BUSYL=READY;

CE0L、R/WL、OEL分別為雙口RAM左端口的片選、讀/寫及輸出使能控制信號(hào)。BUSYL為引至

TMS320F240 READY引腳的信號(hào)。

在右端譯碼電路中,引至TMS320VC33 RDY引腳的信號(hào)為雙口RAM右端口輸出信號(hào)BUSYR,其余邏輯控制信號(hào)編程與左端類似,不再多述。

CY7C028具有64K字的存儲(chǔ)空間,存儲(chǔ)資源較為豐富。系統(tǒng)設(shè)計(jì)時(shí),根據(jù)實(shí)際需要將其前32K字存儲(chǔ)空間作為TMS320F240仿真程序的存儲(chǔ)空間,將其后32K字的存儲(chǔ)空間作為雙DSP的共享數(shù)據(jù)存儲(chǔ)空間。這樣設(shè)計(jì),既減小了電路板面積又簡化了系統(tǒng)的構(gòu)成。在本系統(tǒng)中,CY7C028共享數(shù)據(jù)存儲(chǔ)區(qū)的數(shù)據(jù)確定如下:TMS320F240端為0x8000~0xFFFF,TMS320VC33端為0xC88000~0xC8FFFF。

采用上述接口電路,使得導(dǎo)航計(jì)算機(jī)系統(tǒng)電路簡單、可靠性高,同時(shí)使主從計(jì)算機(jī)之間具有很高的通信速度。經(jīng)實(shí)驗(yàn)測試,在傳輸4K字節(jié)的系統(tǒng)數(shù)據(jù)過程中,其傳輸速率高達(dá)6.6M字節(jié)/秒,能很好地滿足系統(tǒng)導(dǎo)航解算周期為5ms的實(shí)時(shí)性要求。

2.3 雙口RAM的分區(qū)處理及軟件設(shè)計(jì)

利用雙口RAM的BUSY信號(hào)線,雖然可以保證左右兩個(gè)端口能可行地完成數(shù)據(jù)的傳送,但當(dāng)兩個(gè)端口對(duì)同一地址單元同時(shí)存取數(shù)據(jù)時(shí),其中一個(gè)端口要處于等待狀態(tài)。對(duì)于導(dǎo)航系統(tǒng)來說,插入等待狀態(tài)會(huì)降低數(shù)據(jù)交換率,這在一定程度上會(huì)影響系統(tǒng)的實(shí)時(shí)性。為了盡可能地避免出現(xiàn)等待狀態(tài),結(jié)合系統(tǒng)中的數(shù)據(jù)總以幀的方式進(jìn)行數(shù)據(jù)處理的特點(diǎn),在對(duì)雙口RAM編程時(shí),采用了地址分區(qū)方式。即將共享數(shù)據(jù)區(qū)按一定的標(biāo)準(zhǔn)劃分成若干個(gè)數(shù)據(jù)并制定相應(yīng)的軟件協(xié)議,使得主、從機(jī)以適當(dāng)?shù)臅r(shí)序讀寫數(shù)據(jù),從而避免對(duì)同一單元的競用,提高實(shí)時(shí)性。

在本系統(tǒng)中,主、從機(jī)之間需要交換的數(shù)據(jù)主要是與GPS接收機(jī)、彈載計(jì)算機(jī)、火控系統(tǒng)、地面檢測系統(tǒng)進(jìn)行雙向通信的數(shù)據(jù)。軟件分區(qū)處理時(shí),按照交換數(shù)據(jù)的類型將雙口RAM的共享存儲(chǔ)區(qū)從起始單元開始分成四個(gè)大的數(shù)據(jù)區(qū),數(shù)據(jù)區(qū)大小由實(shí)際的數(shù)據(jù)幀長度確定。每個(gè)大數(shù)據(jù)區(qū)又細(xì)分為一個(gè)數(shù)據(jù)接收緩沖區(qū)和一個(gè)數(shù)據(jù)發(fā)送緩沖區(qū),且每個(gè)緩沖區(qū)都定義有相應(yīng)的數(shù)據(jù)存取基地址和讀、寫指針。主、從機(jī)根據(jù)緩沖區(qū)數(shù)據(jù)存取基地址及讀、寫指針,對(duì)相應(yīng)單元進(jìn)行讀、寫操作,整個(gè)緩沖區(qū)等效于一個(gè)環(huán)形數(shù)據(jù)。若緩沖區(qū)大小設(shè)置合理,當(dāng)新數(shù)據(jù)覆蓋舊數(shù)據(jù)時(shí),舊數(shù)據(jù)已經(jīng)處理,既不會(huì)遺漏數(shù)據(jù)又節(jié)省了存儲(chǔ)單元。

在本系統(tǒng)中,所有對(duì)外部系統(tǒng)的通信工作均由從機(jī)TMS320F240通過擴(kuò)展串口ST16C554來完成。考慮到整個(gè)系統(tǒng)的數(shù)據(jù)處理流程及時(shí)序要求,在TMS320F240的軟件設(shè)計(jì)中,數(shù)據(jù)接收采用中斷方式,數(shù)據(jù)發(fā)送則是在軟件的主流程內(nèi)部維持一個(gè)無限循環(huán),將發(fā)送程序駐留在此循環(huán)中,通過查詢發(fā)送緩沖區(qū)的讀、寫指針,實(shí)時(shí)發(fā)送數(shù)據(jù)。ST16C554共有四個(gè)串口,分別負(fù)責(zé)與前述四個(gè)外部系統(tǒng)的數(shù)據(jù)通信。主機(jī)TMS320VC33只需對(duì)雙口RAM中相應(yīng)的數(shù)據(jù)緩沖區(qū)寫入要發(fā)送的數(shù)據(jù)或讀取需要的數(shù)據(jù)即可。鑒于主、從機(jī)對(duì)這四種類型數(shù)據(jù)的存取操作程序類似,在此只給出TMS320F240接收火控系統(tǒng)數(shù)據(jù)和TMS320VC33讀取火控系統(tǒng)數(shù)據(jù)的程序流程圖,分別如圖4和圖5所示。其中,Base為火控系統(tǒng)數(shù)據(jù)接收緩沖區(qū)數(shù)據(jù)存取基地址。

評(píng)論