利用AMSVF進(jìn)行混合信號(hào)SoC的全芯片驗(yàn)證

UPS求解器

一般來(lái)說(shuō),電源/地線網(wǎng)絡(luò)中存在大量的寄生RC,在版圖后仿真時(shí),這些寄生RC將會(huì)大大降低性能,并侵占大量?jī)?nèi)存。對(duì)于這類模擬,AMSVF中的UPS求解器可被用于加速模擬速度,同時(shí)保持精確性。模擬器首先偵測(cè)電源網(wǎng)絡(luò),然后將整個(gè)設(shè)計(jì)分離為電源網(wǎng)絡(luò)和信號(hào)網(wǎng)絡(luò)兩部分。電源網(wǎng)絡(luò)部分由UPS求解器處理,而信號(hào)網(wǎng)絡(luò)部分則由Ultrasim求解器處理。電源網(wǎng)絡(luò)模擬的示意圖如圖2所示。

圖2 電力網(wǎng)絡(luò)模擬法示意圖

使用傳統(tǒng)的瞬態(tài)模擬和UPS求解器分別進(jìn)行電壓降分析的性能對(duì)比如表1所示。

VR技術(shù)

由于芯片內(nèi)電源電壓不斷降低,并開(kāi)始采用多電源電壓,因此,越來(lái)越多的混合信號(hào)/RF或數(shù)字電路均使用片上穩(wěn)壓器來(lái)產(chǎn)生內(nèi)部供電電壓。Ultrasim求解器通過(guò)有效的分區(qū)技術(shù)實(shí)現(xiàn)模擬加速,但這只能應(yīng)用在電路由理想電源電壓驅(qū)動(dòng)的情況下。使用傳統(tǒng)的分區(qū)技術(shù),所有連接到內(nèi)部穩(wěn)壓源的模塊都必須包含在單個(gè)分區(qū)內(nèi),嚴(yán)重影響了模擬速度。

VR(穩(wěn)壓)技術(shù)能夠克服這種限制, 讓用戶能夠方便地對(duì)由內(nèi)部穩(wěn)壓器供電的電路模塊進(jìn)行模擬仿真。

快速包絡(luò)分析

總的來(lái)說(shuō),當(dāng)被調(diào)制電路采用傳統(tǒng)的瞬態(tài)分析時(shí),需要非常小的時(shí)間步長(zhǎng)以適應(yīng)高頻載波信號(hào),并且需要長(zhǎng)時(shí)間的持續(xù)周期覆蓋低頻基帶信號(hào),這將使得模擬變得非常緩慢和困難。快速包絡(luò)分析主要用于解決這個(gè)難題,這些電路類型通常出現(xiàn)在發(fā)射器、接收器等RF電路中。

AMSVF的快速包絡(luò)分析功能提供了對(duì)模擬/混合信號(hào)電路進(jìn)行模擬和設(shè)計(jì)的有效方法。任何包含已調(diào)制信號(hào)的電路或RF部分都可以通過(guò)快速包絡(luò)分析法進(jìn)行模擬,而電路的其它部分則由數(shù)字求解器或傳統(tǒng)的瞬態(tài)模擬法進(jìn)行仿真。包括數(shù)字和模擬電路在內(nèi)的所有仿真都在每個(gè)時(shí)間步長(zhǎng)進(jìn)行同步,它考慮了各仿真之間的耦合,并確保解決方案的精確性。快速包絡(luò)分析可以跳過(guò)時(shí)鐘周期中的很多時(shí)點(diǎn),減少大量的時(shí)間步長(zhǎng)數(shù),簡(jiǎn)化計(jì)算量。

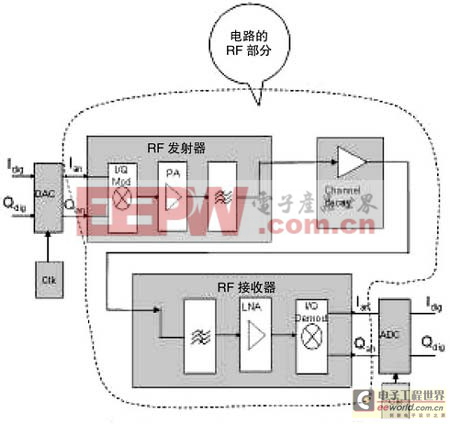

以圖3中完整的RF電路為例,它包含了發(fā)射器、接收器和ADC/DAC Verilog-AMS模塊。與瞬態(tài)分析相比,快速包絡(luò)分析可以通過(guò)極小的精確性損失讓性能提高7倍。兩種方法的波形對(duì)比如圖4所示,來(lái)自快速包絡(luò)的最后一個(gè)波形跳過(guò)了很多周期。

圖3 完整的RF電路和ADC/DAC行為模塊

結(jié)語(yǔ)

AMSVF已經(jīng)被證明是一種針對(duì)復(fù)雜混合信號(hào)電路進(jìn)行全芯片驗(yàn)證的有效而強(qiáng)大的工具。它不僅提供了靈活的應(yīng)用模式,還包括更加先進(jìn)而強(qiáng)大的功能,能夠幫助更多的用戶在設(shè)計(jì)的初期階段發(fā)現(xiàn)設(shè)計(jì)錯(cuò)誤,縮短設(shè)計(jì)周期,實(shí)現(xiàn)一次性流片成功。

評(píng)論