擴頻通信系統CCSK信息調制解調算法設計

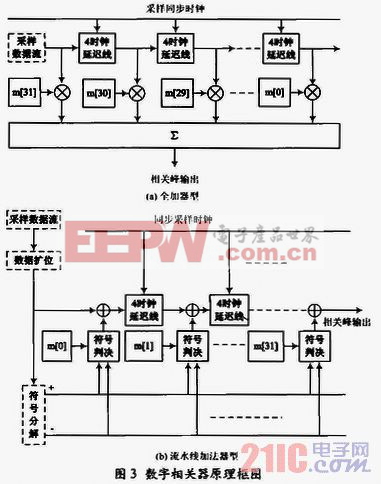

數字相關器是CCSK信息解調的關鍵部件,通過相關器進行CCSK信息解調有兩種不同的邏輯電路架構,包括兩級串聯型相關處理算法電路和多極并行數字相關器。無輪哪種CCSK相關解調器,其核心都是數字相關器,而數字相關器分為全加器型數字相關器和流水線加法器型數字相關器。這兩種數字相關器的原理框圖如圖3所示。

兩級串聯型CCSK相關解調邏輯電路一般由兩個全加器型數字相關器級聯而成。如采用32 bit m序列擴頻碼的系統,可將兩個32 bit相關器級聯成64 bit相關器,其m序列本地碼可設置成兩個同樣的m序列:

{a31,a30,a29,…,a2,a1,a0,a31,a30,a29,…,a2,a1,a0}

當輸入基帶碼流信號為m序列的某一種32 bit循環移位碼時,相關器就會輸出相應的相關峰信號。其過程如下:

輸入基帶碼流為32 bit m序列的原碼時(時間次序為{a31,a30,a29,…,a2,a1,a0}),當碼流與第一段本地碼對應緩沖器內的本地序列{a31,a30,a29,…,a2,a1,a0}一致時,相關器就會輸出第一相關峰;在采樣同步時鐘的驅動下,輸入碼流進入第二段本地碼對應緩沖器內,此后,當碼流與相關器的本地序列{a31,a30,a29,…,a2,a1,a0}一致時,相關器就會輸出第二相關峰。

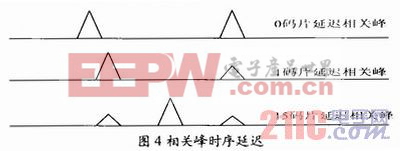

當輸入信號是擴頻碼m序列的1次循環移位碼時,只有當輸入碼流信號被驅動到{a30,a29,…,a2,a1,a0,a31}的位置上時,相關器才輸出相關峰信號。相對于0次循環移位碼產生的相關峰,其時序延遲了一個碼片單位。依次類推,當輸入信號是擴頻碼m序列的N(0≤N≤31)次循環移位碼時,通常可以得到延遲N個碼片時間的相關峰。圖4所示是相關峰時序延遲示意圖。

通過計算相關峰輸出時間同基準(0延遲)相關峰之間的時間差,可以提取調制在信號上的信息數據N:

N=(數據相關峰字符時間-基準相關峰字符時間)/碼片時間

采用兩級串聯型CCSK相關解調邏輯電路解調CCSK信息消耗的硬件資源較少,但由于要對相關峰進行定時檢測以及消除部分相關峰,因此,對電路的處理時序較為嚴格,只能采用全加器型數字相關器來實現。而流水線加法器數字相關器由于不具有實時歸零功能,無法實現兩級級聯,因此不適合兩級串聯型CCSK相關解調邏輯電路的相關器。

通信相關文章:通信原理

評論