基于SRIO協(xié)議的板級(jí)芯片互聯(lián)技術(shù)

軟硬件結(jié)合構(gòu)建寬帶互聯(lián)并行處理的數(shù)據(jù)處理系統(tǒng)是實(shí)現(xiàn)高速實(shí)時(shí)數(shù)據(jù)處理的有效方案。基于這樣的方案設(shè)計(jì)理念,采用多DSP、多FPGA通過(guò)SRIO互聯(lián)來(lái)實(shí)現(xiàn)一個(gè)高速互聯(lián)的計(jì)算網(wǎng)絡(luò),數(shù)據(jù)可以在DSP之間及DSP與FPGA之間高速傳輸。這樣的互聯(lián)計(jì)算網(wǎng)絡(luò)在數(shù)據(jù)交互、任務(wù)切換、算法分解、計(jì)算負(fù)載均衡等方面具有較強(qiáng)的適應(yīng)性、可擴(kuò)展性。本文介紹了這種基于SRIO互聯(lián)技術(shù)的高速實(shí)時(shí)數(shù)據(jù)處理硬件平臺(tái),并在該平臺(tái)上研究了多DSP之間、DSP與FPGA之間的SRIO通信技術(shù)。

1 SRIO標(biāo)準(zhǔn)

RapiclI/O是面向嵌入式系統(tǒng)開(kāi)發(fā)提出的高可靠、高性能、基于包交換的新一代高速互聯(lián)技術(shù),已于2004年被國(guó)際標(biāo)準(zhǔn)化組織(ISO)和國(guó)際電工協(xié)會(huì)(IEC)批準(zhǔn)為ISO/IECDIS 18372標(biāo)準(zhǔn)。SRIO則是面向串行背板、DSP和相關(guān)串行數(shù)據(jù)平面連接應(yīng)用的串行RapidIO接口。串行RapidIO包含一個(gè)3層結(jié)構(gòu)的協(xié)議,即物理層、傳輸層、邏輯層。物理層定義電氣特性、鏈路控制、低級(jí)錯(cuò)誤管理;傳輸層定義包交換、路由和尋址機(jī)制;邏輯層定義總體協(xié)議和包格式。可以實(shí)現(xiàn)最低引腳數(shù)量,采用DMA傳輸,支持復(fù)雜的可擴(kuò)展拓?fù)洌帱c(diǎn)傳輸;可選的1.25 Gbps、2.5 Gbps、3.125 Gbps三種速度能滿足不同應(yīng)用需求,是未來(lái)十幾年中嵌入式系統(tǒng)互聯(lián)的最佳選擇之一。

2 基于C6455高速SRIO接口的互聯(lián)系統(tǒng)

2.1 C6455的SRIO端口

TMS320C6455(簡(jiǎn)稱C6455)是德州儀器(TD公司新推出的一款DSP產(chǎn)品,可實(shí)現(xiàn)更高性能,精簡(jiǎn)代碼,更多片上存儲(chǔ)器及超高帶寬的集成外設(shè)。其中最為引人矚目的是第一次實(shí)現(xiàn)了用于處理器間通信的SRIO總線,C6455上的SRIO端口是面向嵌入式領(lǐng)域推出的具有高數(shù)率,很少引腳的互聯(lián)方案,并且Rapicl I/O的數(shù)據(jù)傳輸完全是由硬件實(shí)現(xiàn)的,不需要處理器參與,因此這樣可以實(shí)現(xiàn)一個(gè)高效板級(jí)同構(gòu)互聯(lián)多處理器系統(tǒng)。C6455的SRIO端口一對(duì)收發(fā)差分信號(hào)對(duì)構(gòu)成一個(gè)全雙工的port(端口),可以工作在1.25 Gbps、2.5 Gbps、3.125 Gbps的波特率。

2.2 基于SRIO的多C6455互聯(lián)結(jié)構(gòu)

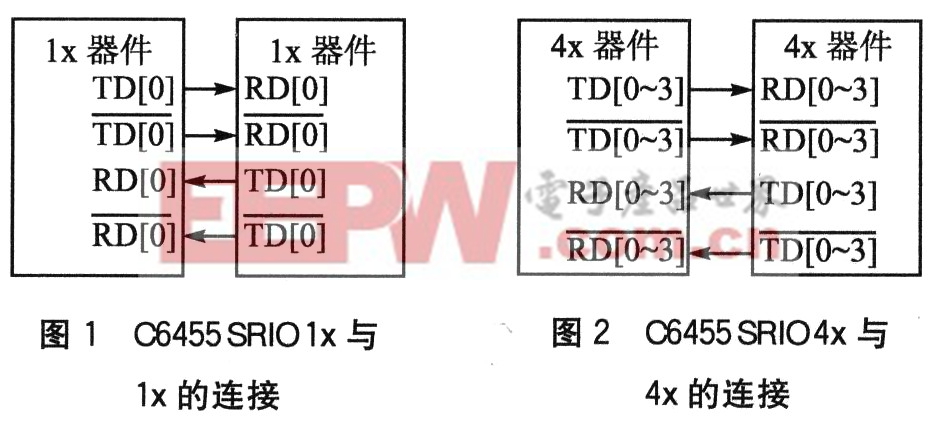

C6455的SRIO端口可以與SRIO交換器件實(shí)現(xiàn)互聯(lián),也可以在C6455之間通過(guò)連接差分信號(hào)來(lái)實(shí)現(xiàn)。如圖1和圖2所示的1x模式和4x模式互聯(lián)關(guān)系,在1x模式中,器件的任何一對(duì)發(fā)收信號(hào)可以與另一個(gè)器件的收發(fā)信號(hào)相互連接組成獨(dú)立的1x模式工作。如果兩個(gè)C6455間采用四對(duì)全連接方式,則可實(shí)現(xiàn)1個(gè)4x工作模式或者是4個(gè)獨(dú)立的1x工作模式。

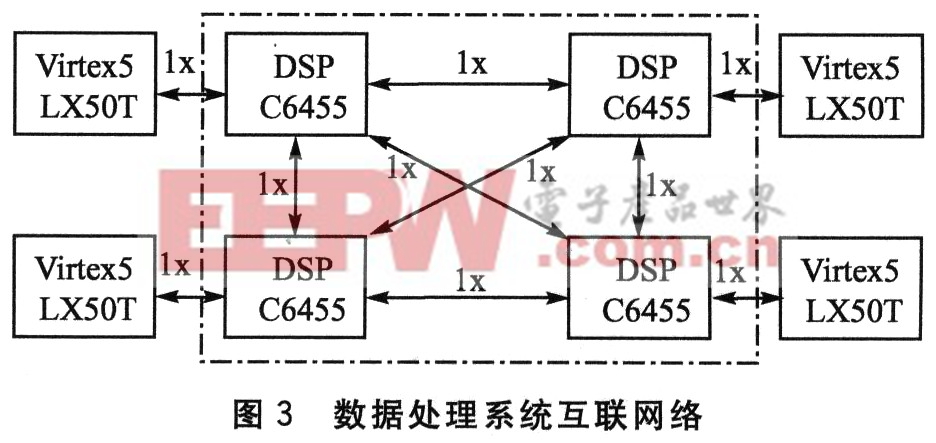

多DSP及FPGA的并行處理系統(tǒng)主要由4個(gè)C6455處理器和4個(gè)Virtex5LX50T構(gòu)成,系統(tǒng)結(jié)構(gòu)如圖3所示。DSP與DSP之間的互聯(lián)采用圖1所示的連接方式來(lái)實(shí)現(xiàn)全連通的SRIO網(wǎng)絡(luò),實(shí)現(xiàn)所有DSP之間的1路1x通道,各個(gè)通道上的控制、傳輸獨(dú)立并行工作。通過(guò)SRIO互聯(lián)網(wǎng)絡(luò),任何一個(gè)DSP C6455都可以訪問(wèn)網(wǎng)絡(luò)上其他DSPC6455資源,實(shí)現(xiàn)網(wǎng)絡(luò)上的所有設(shè)備資源共享。而且這樣的全連通結(jié)構(gòu)又可以根據(jù)不同任務(wù)處理的特點(diǎn),靈活地配置成菊花鏈串行流水線、一主多從的星形等拓?fù)浣Y(jié)構(gòu),在不同數(shù)據(jù)處理應(yīng)用中具有高度可動(dòng)態(tài)重構(gòu)性。

評(píng)論