基于FPGA-SPARTAN芯片的CCD的硬件驅(qū)動電路設(shè)計

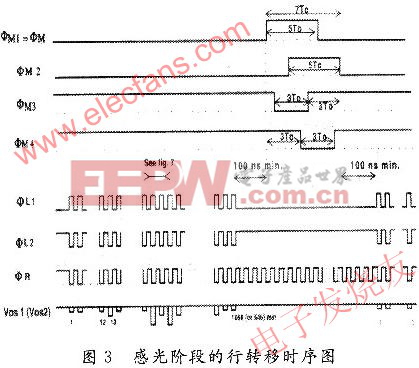

在感光階段即A的上升沿階段,P1,P2,P3,P4保持不變,感光陣列和幀存儲區(qū)之間為阻斷態(tài),兩者之間不會發(fā)生電荷轉(zhuǎn)移現(xiàn)象。但感光陣列接受外界光源照射會積累電荷,在電荷積累的同時,在讀出寄存器時鐘L1,2的控制下,會首先讀出一行電荷。當讀完第1行信號之后,會進行1次行轉(zhuǎn)移。在寄存器時鐘的控制下,寄存器時鐘M1中的信號會轉(zhuǎn)移給寄存器M2,然后再次轉(zhuǎn)移到寄存器M3,M4。行轉(zhuǎn)移時,讀出寄存器時鐘L1,L2不變,無像元信號輸出。在行轉(zhuǎn)移結(jié)束之后,進行第2行電荷的讀出;每讀出1行信號,進行1次行轉(zhuǎn)移,如圖3所示,如此循環(huán)1056次則感光階段完成。轉(zhuǎn)移階段即為門控時鐘A的下降沿階段,如圖4所示。幀轉(zhuǎn)移控制信號P1,P2,P3,P4與行轉(zhuǎn)移控制信號M1,M2,M3,M4相同,且一直有效。讀出寄存器時鐘L1,L2無效,不輸出數(shù)據(jù)。在幀轉(zhuǎn)移結(jié)束之后,進入感光階段,存儲區(qū)首先進行1次行轉(zhuǎn)移,開始信號的輸出,同時感光區(qū)像元進入電荷積累。這樣就構(gòu)成了TH7888A工作的1個周期。

主時鐘脈沖周期定為50 ns,然后主時鐘通過4分頻產(chǎn)生L和R。L作為基礎(chǔ)波形會在以后產(chǎn)生和控制L1,L2和M類波形時使用,L的占空比為2:2,R的占空比為3:1。給L建一個循環(huán)記數(shù)器CL,它的范圍為0~1 065,在感光階段即A的上升沿階段當CL小于1057的時候L1=L其余階段L1為低電平,L1取反為L2;當1057

評論