基于FPGA-SPARTAN芯片的CCD的硬件驅動電路設計

CCD驅動電路的實現是CCD應用技術的關鍵問題。以往大多是采用普通數字芯片實現驅動電路,CCD外圍電路復雜,為了克服以上方法的缺點,利用VHDL硬件描述語言.運用FPGA技術完成驅動時序電路的實現。該方法開發周期短,并且驅動信號穩定、可靠。系統功能模塊完成后可以先通過計算機進行仿真,再實際投入使用,降低了使用風險性。

本文引用地址:http://www.104case.com/article/151547.htm1 硬件設計

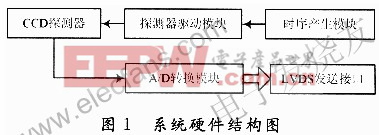

CCD的硬件驅動電路系統的核心器件是SPARTAN系列芯片XC3S50;CCD采用Atmel公司的CCDTH7888A圖像傳感器;CCD驅動脈沖由XC3S50提供,脈沖信號產生后由驅動模塊對脈沖電壓進行變換使其符合TH7888A的驅動電壓要求。CCD像素輸出電壓經過A/D轉換模塊處理電路VSP2272芯片的處理得到數字信號,最后為了方便傳輸和方便后續模塊對數字信號的處理將數字信號由TTL電平轉換成LVDS電平進行輸出,整個系統如圖1所示。

1.1 TH7888A簡介

CCD圖像傳感器采用THOMSON公司生產的TH7888A。它是一種高性能的幀轉移面陣CCD器件,采用四相脈沖驅動工作,并提供電子快門的功能;同時,它具有2種輸出的模式:單路輸出和雙路輸出。其主要的性能參數如下:

光敏區和存儲區均為1024×1024像素;速度可以達到30 images/s以上;像元尺寸為14 mm×14 mm;感光區面積為14.34 mm×14.34 mm;光譜波長范圍在400~700 nm之間;像元輸出頻率為20 MHz。

1.2 XC3SC50簡介

XC3S50屬于XILINX公司SPARTAN3系列的FPGA(現場可編程邏輯門陣列),是一種高性能器件,其特點是:器件運用90 μm加工技術;具有高性能低功耗的特點;邏輯密度達1 728個可用門;3路電源供電即I/O端口供電為1.2~3.3V,核心供電1.2V,輔助功能供電2.5V;帶有2 KB容量分布式RAM和7KB容量的BLOCK RAM,高級的邏輯時鐘管理功能。Ahera公司QuartusⅡ開發系統提供應用設計支持。

2 軟件設計

CCD驅動時序用VHDL描述。VHDL是可以描述硬件電路功能、信號連接關系的語言,其具有比電路原理圖更有效地表示硬件電路的特點。由于它與硬件電路無關等優點,用來設計電路時可大大提高開發效率。

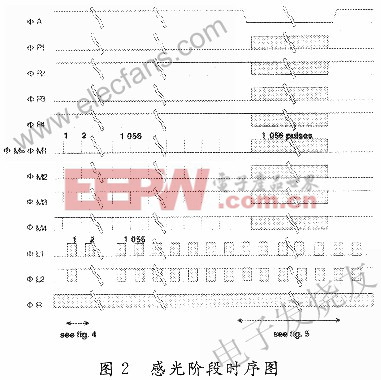

由芯片的結構可以知道,CCD的1個周期分成感光和轉移2個階段,如圖2所示。

感光階段即A的上升沿階段,主要實現3個功能:感光陣列的電荷積累,幀存儲區到轉移寄存器的電荷轉移以及轉移寄存器向輸出放大器的電荷輸出(即行轉移);轉移階段即A的下降沿階段,主要完成感光陣列所積累的電荷向幀存儲區的轉移(即幀轉移),同時清空幀存儲區的無效電荷。其具體的工作過程分析如下:

評論