PLD和數據通路來釋放微控制器中CPU資源

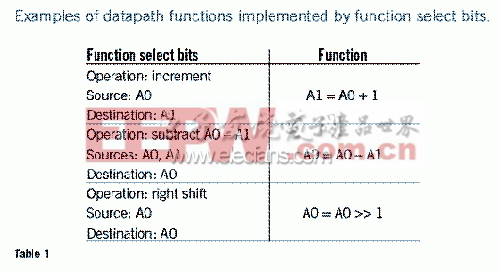

根據數據通路的具體設計,其可能會做一系列復雜操作,如表1顯示。

這個函數選擇模塊實際上可以是一個小容量的SRAM,預加載所需的函數選擇位,SRAM的地址線可以用來選擇運行哪個操作。最后,多數據通路可以用進位和移位信號鏈在一起,以便可以進行多字節操作數。

由于數據通路只有少數特定功能函數,很容易優化設計,因此其創建成本較低。然而,對于實現復雜的邏輯,數據通路遠遠沒有PLD那么靈活。那么,對于創建智能、靈活、低成本的數字外設來說,哪一種方法是更好的呢?是PLD還是數據通路?答案是,將兩者相結合。下面是一個實例,來看看是如何實現的。

通用數字模塊

同時使用PLD和數據通路的系統實例是賽普拉斯半導體的PSoC3和PSoC5芯片。每個系統包含最高24個通用數字邏輯子系統,稱為通用數字模塊(UDB),其結構如圖3所示。一個UDB包含兩個圖1所示的PLD,一個數據通路以及狀態機和控制寄存器。有兩個鏈路路徑,一個用于PLD,一個用于數據通路。由一個路由通道來連接各UDB子塊之間以及UDB之間的信號。PLD配置、數據通路和路由通過寫入UDB配置寄存器來實現。

UDB的PLD設計在圖1中進行了描述。如圖4,UDB數據通路類似于圖2所示的基本的數據通路,但是它更精密復雜,因為擁有更多寄存器和更多的功能。

圖4:UDB數據通路框圖。

* 8位ALU可以實現所有的七個基本函數—遞增、遞減、加、減、與、或以及異或,并且它有單獨的位移和位掩碼模塊來進行ALU結果后處理(8位ALU傳輸功能只需通過ALU傳送一個值到位移和位掩碼模塊)。位移模塊可以做左位移、右位移、半字節交換和傳輸。掩碼模塊可以和單獨的掩碼寄存器里的內容逐位相與(圖中未顯示)。

* 操作可以使用兩個累加器(A0,A1)和兩個數據寄存器(D0,D1)來完成。兩個FIFO寄存器(F0、F1)可用來在數據通路和CPU之間傳輸數據。FIFO深度可達4字節。這一結構可以使多任務處理變得簡單;在不同的時間,獨立操作可以在寄存器子集完成。例如,A0、D0、F0可以用于一個任務,而A1、D1、F1則可用于不同的任務。

* 廣泛的狀態條件(例如:比較、零檢測、所有個體檢測、溢出檢測)可以應用到累加器,數據寄存器,以及路由到器件其它地方。

評論