使用LDO和PLD實現電源啟用和禁用功能

許多系統需要通過控制線或在施加輸入電源時啟用和禁用。雖然小型微控制器 (MCU) 可以實現啟用/禁用功能,但您仍然需要為其編寫、維護和燒錄代碼。許多使用片上系統 (SoC) 的設計在該芯片內都有一個 MCU;添加另一個是多余的。此外,SoC 中的 MCU 不夠低功耗,無法保持始終開啟并提供啟用控制器功能。

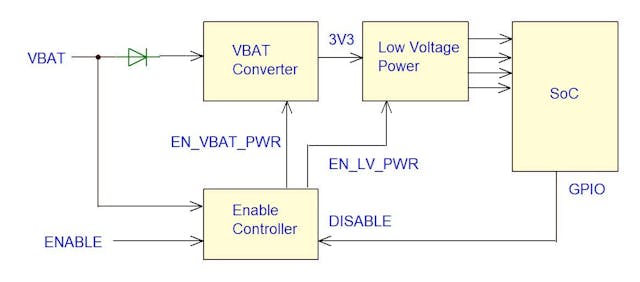

本文引用地址:http://www.104case.com/article/202504/469655.htm本文討論了一種低成本、低功耗的使能控制器硬件解決方案,該解決方案使用低壓差線性穩壓器 (LDO) 和可編程邏輯器件 (PLD),僅消耗微安級電流。PLD 預編程了實現使能控制器決策功能所需的邏輯。圖 1 顯示了建議的解決方案;其電源通常用于為 SoC 供電的汽車系統。

圖1. 說明 SoC、電源和使能控制器的基本系統圖。啟用控制器解決方案

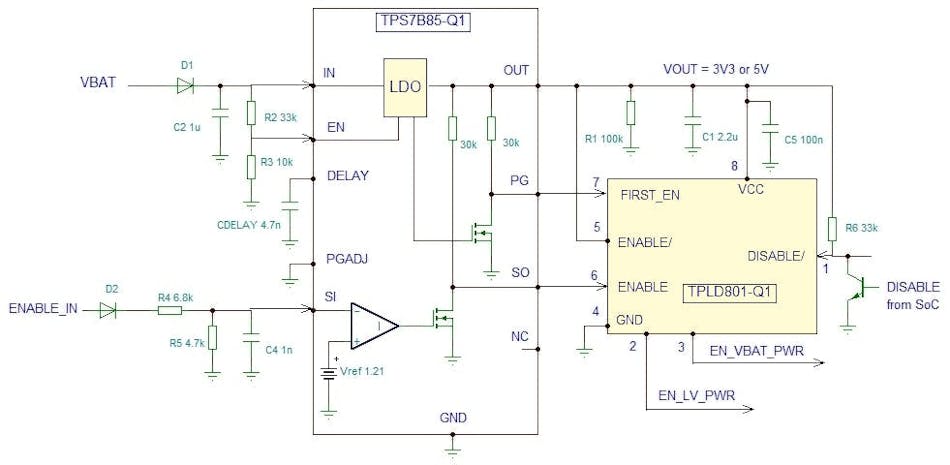

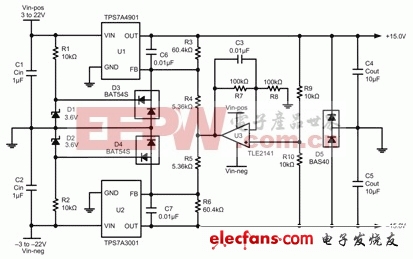

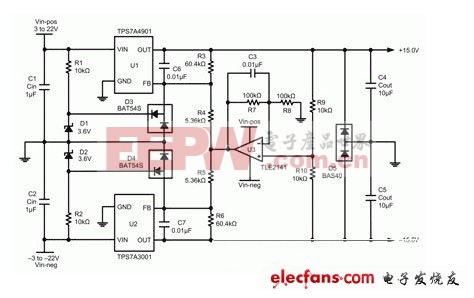

該解決方案采用 TPS7B85-Q1 電池斷續 LDO1 和 TPLD801-Q1 PLD2(圖 2)。TPS7B85-Q1 中的功能在此應用中特別有用:

基本 LDO 功能從高達 40V 的電池電壓 (VBAT) 提供固定的 3.3V 或 5V 輸出電壓 (VOUT)。此 VOUT 為 TPLD801-Q1 供電。

具有引腳可編程延遲的電源就緒 (PG) 輸出。當施加 VBAT 時,LDO 上電。當 LDO VOUT 達到穩壓時, PG 在 DELAY 引腳上的電容器編程的延遲后變為高電平。TPLD801-Q1 使用上升的 PG 信號來檢測和鎖存 VBAT (FIRST_EN) 的初始應用以啟用系統。

如果非專用 SENSE 比較器的感應輸入引腳(SI 引腳)分別高于或低于 1.21 V 內部電壓基準 (VREF),則提供邏輯高電平或低電平檢測輸出(SO 引腳)。SI 引腳的最大電壓為 40 V,無論 LDO VIN 是否通電。對于阻斷負電壓,您可以使用二極管 D2。比較器測試ENABLE_IN信號的幅度是否高于某個電壓閾值。如果是,則允許 signal 傳遞到 TPLD801-Q1 的 enable input。該電壓閾值可通過 R4 和 R5 進行調節。

一個精密使能 (EN) 引腳。精密使能功能(與邏輯電平使能相反)未記錄在 TPS7B85-Q1 數據表中,但 EN 引腳連接到具有 1.32 VV REF 閾值(上升)和 100 mV 遲滯的比較器。它允許使用從 VBAT 到 EN 再到接地的電阻分壓器 (R2, R3) 來設置精確的 VBAT 啟動電壓。使用精密使能可確保 LDO 的輸出不會隨著 VBAT (具有未知的斜坡速率)而斜坡上升,而是等到 VBAT 高于設定的啟動電壓后再打開 LDO。在這種情況下,VOUT 在大約 240 μs 內上升,與 VBAT 斜坡速率無關。從所示的電阻值來看,LDO 的 VBAT 啟動電壓約為 6.5 V,但可通過 R2 和 R3 進行調節。VOUT 的斜坡速率很重要,因為 TPLD801-Q1 的最大(最慢)允許 VCC 斜坡速率為 0.25 V/ms。

圖2. 這是使能控制器的原理圖。

泄放電阻 R1 在掉電期間對 LDO (C1) 的輸出電容器放電。TPS7B85-Q1 的 PG 和 SO 引腳上具有 30kΩ 內部上拉電阻器。PG delay 的長度是一個選擇問題。CDELAY = 4.7 nF 的延遲約為 4 ms(圖 2)。

TPLD801-Q1 的一些設計說明

TPLD801-Q1 是一款符合汽車標準的 PLD,集成了觸發器、計數器、延遲、邏輯門和 25 kHz 或 2 MHz 振蕩器等邏輯模塊,以及分頻器和流水線延遲。TI 的 InterConnect Studio 設計工具可以圖形方式設計和仿真邏輯設計。

您還可以使用 TPLD801 評估模塊和 TPLD 編程器套件將邏輯設計永久編程到一次性可編程存儲器中,或將設計臨時編程到易失性寄存器中。

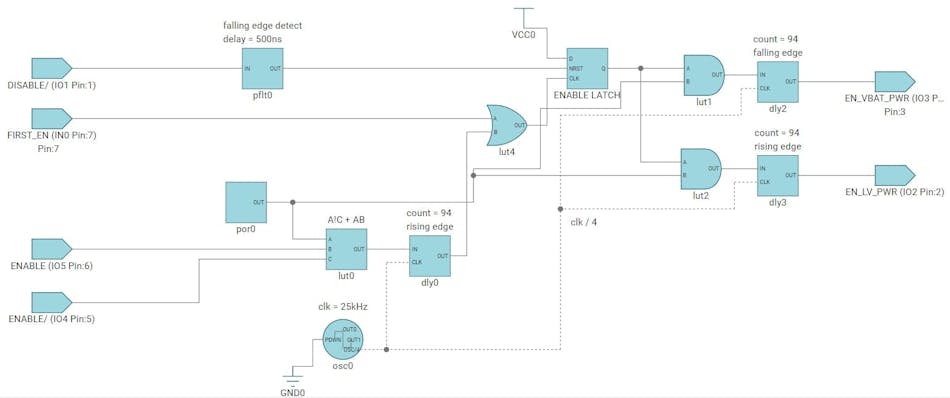

TPLD801-Q1 logic design 的核心是一個配置為 latch (ENABLE LATCH) 的 D 型 flip-flop,因此 rising clock edge 鎖存一個 logic-high output。只有 reset input 可以重置 latch。鎖存器輸出進入兩條單獨的延遲線,每條延遲線設置為大約 15 ms。當鎖存器輸出變為高電平時,EN_VBAT_PWR信號立即變為高電平并啟用前端電源。

為了留出時間讓前端首先上電,EN_LV_PWR信號在大約 15 毫秒后變為高電平,并使能為 SoC 和系統其余部分供電的電源。

可以通過兩種方式為 ENABLE LATCH 提供 rising edge 的時鐘:

在第一個使能事件中,在 LDO 的 PG 輸出上產生一個上升沿。

使用 ENABLE 信號從 TPS7B85-Q1 的 SO 輸出傳遞到 PLD,并且 PLD 測量的內容比預編程的持續時間長。或者,如果您需要不同的應用程序,您可以使用反向 ENABLE/ 信號;但如果不使用,它就會被綁得很高。

在第二種情況下,為了抑制雜散噪聲信號,PLD 通過延遲線來測量輸入的 ENABLE 信號是否足夠長,該延遲線由 PLD 的內部 25 kHz 除頻振蕩器計時。25 kHz 振蕩器的功耗非常低,功耗為 8.2 μA。

延遲線計數 94 的總延遲約為 15 毫秒,但您可以根據應用程序的要求將此時間設置為不同的持續時間。如果在此延遲期間和之后輸入的 ENABLE 信號仍然存在,則延遲線的輸出變為高電平,這會為 ENABLE LATCH 的 clock 提供上升沿并鎖存一個邏輯高電平。如果輸入的 ENABLE 信號在整個時間內都不存在,則 delay counter 將重置,并且不會發生 latch 的上升沿。

當電子控制單元需要斷電時,SoC 的 MCU 通過通用輸入/輸出發出上升沿。該 DISABLE 信號連接到圖 1 所示的漏極開路晶體管,并下拉 PLD 的 DISABLE/ 引腳以重置 ENABLE LATCH。ENABLE LATCH 復位后, EN_LV_PWR 輸出立即變為低電平;大約 15 ms 后,EN_VBAT_PWR 輸出變為低電平。

這個 15 毫秒的延遲使低壓電源軌能夠在前端電源被禁用之前按照 SoC 要求的正確順序進行降序。EN_VBAT_PWR 和 EN_LV_PWR 上升或下降之間的延遲時間可以通過更改延遲線的數量來配置。

選擇 PLD 輸入作為施密特觸發器輸入,為驅動到它們的 logic signals 需要多快轉換提供了余地。兩個使能輸出信號配置為推挽式。(如果使用開漏,則此配置會在上電時產生毛刺,因為在 TPLD801-Q1 的一次性可編程存儲器 OTP 加載并將輸出配置為開漏之前,開漏輸出被上拉電阻器暫時拉高。即使使用推挽式,在 OTP 存儲器加載之前,輸出也是高阻抗的;因此,您可能需要外部 pull-down 電阻器。圖 3 顯示了整體 PLD 設計。

圖3. 此圖顯示了 TPLD801-Q1 的內部結構。PLD/LDO 組合的基準測試結果

圖3. 此圖顯示了 TPLD801-Q1 的內部結構。PLD/LDO 組合的基準測試結果

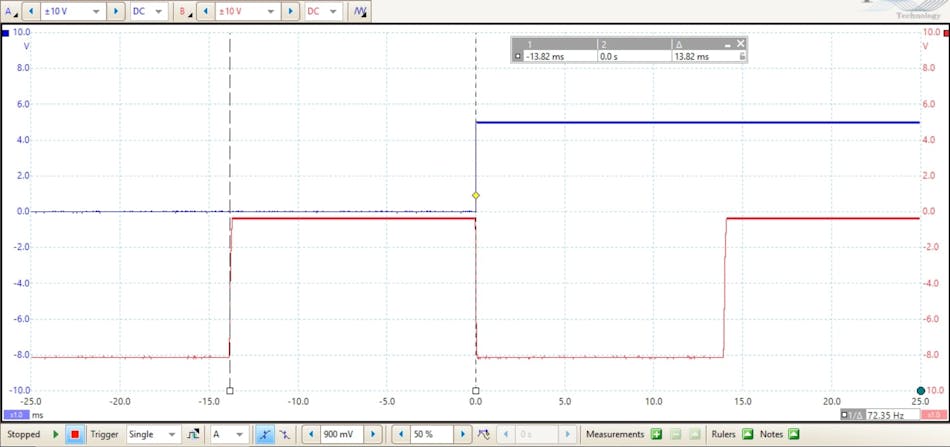

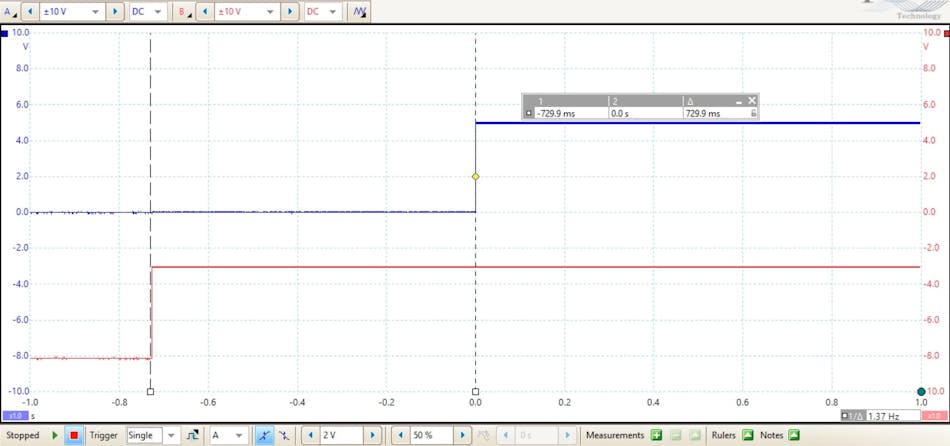

圖 4 顯示了施加到使能控制器的 18 V ENABLE_IN信號,該信號的幅度肯定使 TPS7B85-Q1 比較器能夠將其傳遞到 PLD。該信號還具有足夠的持續時間,以便 PLD 驗證檢測。ENABLE LATCH 響應此 ENABLE_IN 信號而鎖定為高電平,即使 ENABLE_IN 被切換,它也保持高電平。

圖4. 將 18 V ENABLE_IN信號施加到使能控制器,該信號肯定具有允許 TPS7B85-Q1 比較器將其傳遞到 PLD 的幅度。用于 18 V ENABLE_IN信號的 TPS7B85-Q1 SI 引腳電壓以紅色顯示,ENABLE LATCH 內部 PLD 電壓以藍色顯示。

圖4. 將 18 V ENABLE_IN信號施加到使能控制器,該信號肯定具有允許 TPS7B85-Q1 比較器將其傳遞到 PLD 的幅度。用于 18 V ENABLE_IN信號的 TPS7B85-Q1 SI 引腳電壓以紅色顯示,ENABLE LATCH 內部 PLD 電壓以藍色顯示。

在另一個極端情況下,可以成功地對低幅度的 3.4 V 信號重復此測試。或者,您可以對持續時間短、振幅低的 ENABLE_IN 信號重復測試,或者兩者兼而有之,這些信號的持續時間或振幅不足以觸發 ENABLE LATCH 為高電平。

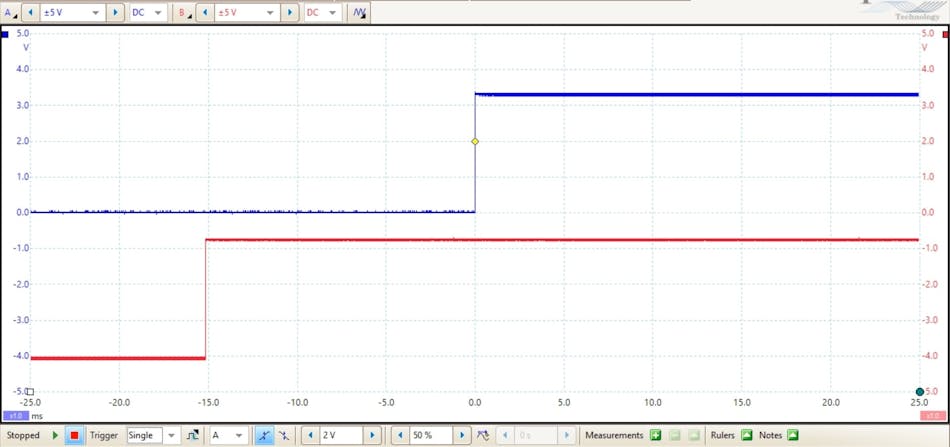

圖 5 顯示了首次將輸入電源施加到 LDO 時的電路行為。當 LDO 調節時,PG 引腳變為高電平,經過延遲 (由 CDELAY 設置) 后,PLD 檢測到第一個上電事件,并且 ENABLE LATCH 鎖存為高電平。(此測試使用評估板的默認 1 μF CDELAY 電容器,其延遲要長得多。

圖5. 此圖顯示了首次將輸入電源施加到 LDO 時的電路行為。TPS7B85-Q1 PG 引腳電壓在首次上電時顯示為紅色,ENABLE LATCH 電壓顯示為藍色。

圖5. 此圖顯示了首次將輸入電源施加到 LDO 時的電路行為。TPS7B85-Q1 PG 引腳電壓在首次上電時顯示為紅色,ENABLE LATCH 電壓顯示為藍色。

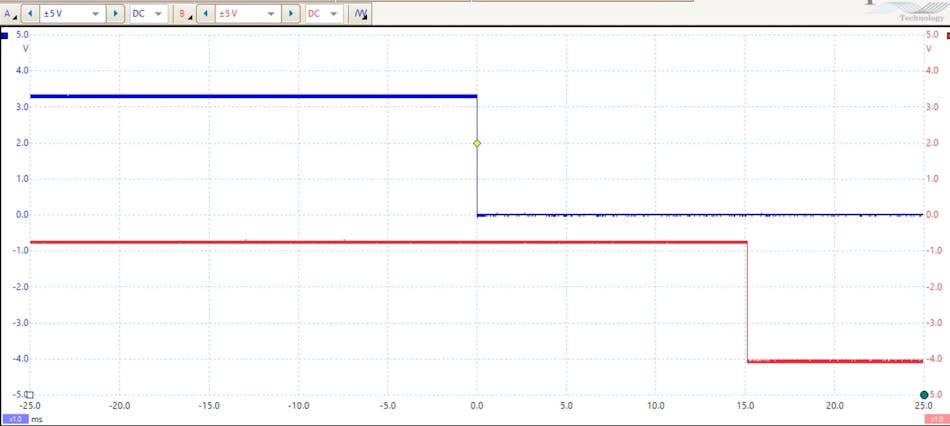

PLD 的實際輸出如圖 6 所示,包括上電序列期間大約 15 ms 的延遲。

圖6. 這些是 PLD 的實際輸出,包括上電序列期間大約 15 ms 的延遲。EN_VBAT_PWR 輸出以紅色顯示,EN_LV_PWR 的 PLD 輸出以藍色顯示。

圖6. 這些是 PLD 的實際輸出,包括上電序列期間大約 15 ms 的延遲。EN_VBAT_PWR 輸出以紅色顯示,EN_LV_PWR 的 PLD 輸出以藍色顯示。

圖 7 顯示了 DISABLE 事件期間的 PLD 輸出,描述了 15 ms 的延遲。

圖7. 這將突出顯示睡眠行為,顯示 EN_LV_PWR(藍色)變為低電平,然后是 EN_VBAT_PWR 信號(紅色)。

圖7. 這將突出顯示睡眠行為,顯示 EN_LV_PWR(藍色)變為低電平,然后是 EN_VBAT_PWR 信號(紅色)。

為什么 PLD/LDO 組合優于微控制器

這種基于硬件的低成本、低功耗解決方案用于處理電源啟用和禁用功能,無需外部 MCU,并且可以進一步定制。您還可以選擇訂購預編程了 logic design 的定制 PLD。

預編程的 PLD 避免了為 MCU 編寫和維護固件的時間和成本。此外,它避免了在生產環境中對 MCU 進行編程。具有預編程 PLD 的這些省時功能以及 TPLD801-Q1 和 TPS7B85-Q1 硬件解決方案成本低的事實節省了整體系統費用。

TPLD801-Q1 采用 1.6 × 2.1 mm 的小封裝,TPS7B85-Q1 采用 3 × 3 mm 封裝,可節省整個印刷電路板布局的空間。這對于印刷電路板設計人員很有幫助,因為他們經常面臨必須在同一電路板區域內安裝更多功能的任務。

評論