PLD和數據通路來釋放微控制器中CPU資源

本文介紹了一種采用PLD和數據通路(datapath)來解放微控制器系統中CPU任務的方案。在大多數微控制器結構中,智能的CPU身邊總會環繞著一系列不可編程的外設。外設的功能有限,通常它們只負責數據形式的轉換。例如,I2C外設只是實現串行和并行數據格式之間的轉換,而ADC則實現模擬到數字信號的轉換。CPU因此不得不完成所有的數據處理工作,實際上它還能做些更有用的事情。此外,管理外設將會導致CPU固件異常復雜,并可能需要一個快速高效的CPU在實時的時序限制下執行這些固件。這又會導致更多的潛在程序漏洞,從而需要使用更復雜和昂貴的調試設備等。

本文引用地址:http://www.104case.com/article/150055.htm但是如果外設具備足夠的復雜度、靈活度與智能,是否能有效地減輕CPU的許多任務呢?本文將展示如何把智能、靈活、低成本、可定制的數字外圍設備設計到微控制器并配置,以幫助實現穩定的分布式系統設計。

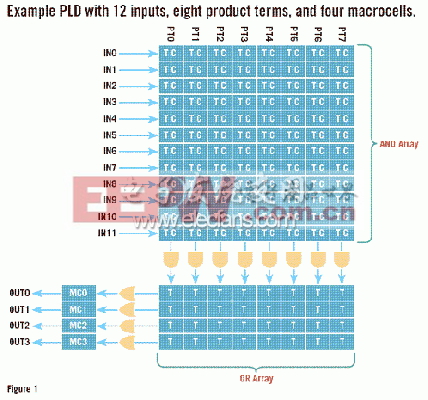

通常有兩種方法構建一個智能的可配置外設。首先是使用PLD。如圖1所示,PLD有一個驅動若干宏單元的積和(sum of products)邏輯門陣列。“T”和“C”符號表示每一個乘積項都能產生一個真值或補數(反向)輸出,這樣無論是正、負邏輯都可以支持。

圖1:一個PLD實例(包括12個輸出項、8個乘積項、4個宏單元)。

圖1顯示了一個簡單的PLD例子。PLD可以有成百上千的宏單元,每個宏單元最高由16個乘積項驅動。乘積項里的與門和或門可以互聯形成高度靈活的定制邏輯功能。宏單元是典型的時鐘架構,它們的輸出可以反饋到乘積項陣列,因此允許創建狀態機。

大規模PLD可以用來形成復雜的邏輯功能,甚至是完全的CPU,因此PLD當然可以用來實現智能數字外設。然而,很多門可能只是實現諸如計數器或加法器等簡單的邏輯功能,但對于更復雜功能的實現,基于PLD的方案就會變得很貴。從某種程度上說,使用真正的CPU會更合理。

CPU的一個非常簡單的形式是基于算術邏輯單元(ALU)的數據通路,也稱為納米處理器(nano-processor)。數據通路只是實現幾個常用函數,但會比使用PLD實現的效率更高。圖2:顯示了一個基于ALU的簡單的數據通路。典型的ALU可以進行各種操作,通常是8位操作:向上計數(遞增)、向下計數(遞減)、加、減、邏輯與、邏輯或、邏輯異或,左位移、右位移。這里有兩個8位累加器,它們能夠為ALU輸出充當輸入數據寄存器或存儲器。一個輸入時鐘信號沿產生一次操作。函數選擇寄存器用來控制:

圖2:基于ALU的數據通路。

* 產生什么操作。

* 該操作的源寄存器。

* 輸出的目的寄存器。

評論