系統芯片ZSU32在SoC芯片設計中的應用

本文針對中山大學ASIC設計中心自主開發的一款系統芯片ZSU32,以Synopsys公司的Design Compiler為綜合工具,探索了對SoC芯片進行綜合的設計流程和方法,特別對綜合過程的時序約束進行了詳細討論,提出了有效的綜合約束設置方案。

本文引用地址:http://www.104case.com/article/148780.htm1 時序約束原理

同步電路是大多數集成電路系統的主流選擇。同步電路具有工作特性簡單、步調明確、抗干擾能力強等特點。但是,因為所有的時序元件受控于一個特定的時鐘,所以數據的傳播必須滿足一定的約束以便能夠保持與時鐘信號步調一致。

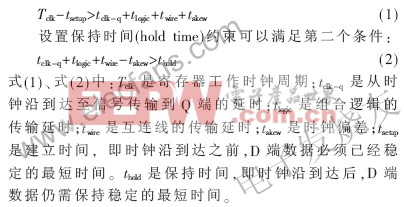

設置建立時間(setup time)約束可以滿足第一個條件:

ZSU32芯片內置32 bit MIPS體系處理器作為CPU,具備兩路獨立的指令和數據高速緩存,CPU內部有獨立的DSP協處理器和浮點協處理器,同時集成了LCD控制器、MPEG硬件加速器、AC97控制器、SRAM控制器、NAND Flash控制器、SATA高速硬盤控制器、以太網MAC控制器等,并具有I2C、I2S、SPI、、UART、GPIO等多種接口模塊。

3 ZSU32系統芯片的約束設置與邏輯綜合

ZSU32系統芯片的綜合采取自底向上的策略,先局部后整體。首先將當前工作層次設置為系統芯片的某個子模塊,然后對該子模塊添加各項具體約束,接著完成子模塊的綜合。依次對各子模塊重復上述綜合流程,當各個模塊都順利通過了初次綜合后,通過set_dont_touch_network命令將模塊中的關鍵路徑和時鐘線網保護起來,然后做一次全局優化,檢查是否滿足時序等各方面的設計要求,達到要求就可以輸出最終的網表和各項綜合報告。

3.1 設定工藝庫和參考庫

設置Design Compiler運行所使用的庫:目標庫(target_library)、鏈接庫(link_library)、可綜合庫(synthetic_library)、符號庫(symbol_library)。其中的目標庫中包含了標準單元庫、RAM單元庫、I/O單元庫、PLL單元庫等,通常是由芯片代工廠家提供。系統芯片ZSU32采用的是中芯國際的0.18 ?滋m CMOS工藝庫,所以在設置時就把目標庫指向該工藝庫。

#設置目標工藝庫

set target_library SMIC.db

3.2 讀入RTL設計與設置工作環境

讀入RTL設計通常有自頂向下或者自底向上2種方式。因為ZSU32模塊眾多,所以采用自底向上的讀入方式。首先讀入各個子模塊,并分別編譯;然后更改層次,編譯上一層的模塊;最后會合成整個系統。

讀入設計后,首先設置芯片的工作環境,根據采用的工藝庫提供的環境和線網負載模型,可以通過set_operating_condition和set_wire_load_model命令進行設置。以下是ZSU32綜合環境的頂層環境設置:

#設置工作環境

set_operating_condition smic18_typ;

#設置線網負載模型

set_wire_load_model smic18_wl30;

3.3 時序約束

3.3.1 時鐘定義

時鐘是整個時序約束的起點。系統芯片ZSU32將外部輸入時鐘和PLL模塊輸入時鐘作為源時鐘:ext_clk_i和pll_clk_i。通過對這2個源時鐘信號的分頻或者倍頻,產生了各個子模塊的時鐘信號。

#定義源時鐘ext_clk,周期16 ns

create_clock-name ext_clk-period

16 [get_ports {ext_clk_i}];

在SoC芯片內部,子模塊的時鐘實際是經過源時鐘分頻或者倍頻得到的,使用create_generated_clock命令來建立子模塊時鐘。

#設置一個2倍頻時鐘clk_main,

#其源時鐘是pll_clk_i

create_generated_clock -name clk_main

-multiply_by 2 -source pll_clk_i;

評論