用于SOC或塊級時鐘的可配置分頻器

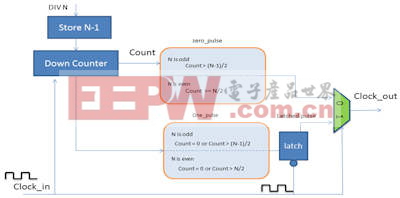

一旦存儲(N-1)寄存器值達(dá)到零,倒數(shù)計數(shù)器將被初始化。電路中的鎖存器確保“NOR”門輸出產(chǎn)生的使能只有在時鐘為低時被傳播到AND門。如果沒有鎖存器,輸出時鐘可能產(chǎn)生故障。

優(yōu)勢:

* 對于基于時鐘門控的分頻器,RTL是相當(dāng)簡單的,另外,穿通時鐘方案顯著減少了高速時鐘DFT復(fù)雜性。

局限性:

* 某些IP,如DDR,要求占空比為50%,這對于穿通時鐘是不可能實現(xiàn)的。

* 從時鐘上升沿開始到時鐘下降沿結(jié)束的時序路徑必須在1/2的時鐘頻率處相遇,也就是說,STA團隊必須在時鐘架構(gòu)確定前,檢查設(shè)計中這些關(guān)鍵時序路徑。

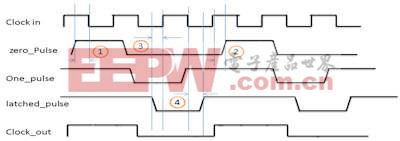

基于多路選擇器的分頻器

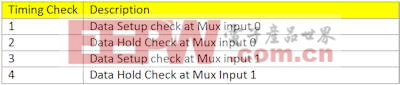

基于多路選擇器的分頻器的實現(xiàn)如下所示,隨附進(jìn)行三分頻時的波形樣本。基于多路選擇器的分頻器讓時鐘流經(jīng)2:1多路選擇器的選擇引腳。多路選擇器數(shù)據(jù)引腳的使能值隨著輸入時鐘切換,使得多路選擇器輸出產(chǎn)生的邏輯正是所需的時鐘輸出。這類實施需要一個重要的條件。在多路選擇器的數(shù)據(jù)輸入端,需要添加額外的時鐘門控檢查,確保時鐘分頻器電路正常工作。下面的波形中顯示了時序檢查。

本文引用地址:http://www.104case.com/article/148205.htm

本文引用地址:http://www.104case.com/article/148205.htm

圖6:基于多路選擇器的分頻器。

以下波形在對輸入時鐘進(jìn)行三分頻時生成。

圖7:3分頻波形。

圖8:時序檢查。

時序檢查1是從時鐘上升沿到時鐘下降沿的半周期設(shè)置檢查,因此如果輸入時鐘被鎖定在極高的頻率,這項檢查將至關(guān)重要(例如為最大程度地減少抖動,將鎖相環(huán)輸出鎖定在極高的頻率。)

RTL復(fù)雜性低,通常由設(shè)計人員選擇是否采用50%占空比的時鐘分頻器。

優(yōu)勢:

* 50%占空比的整數(shù)分頻和不具有50%占空比的分?jǐn)?shù)分頻

* 所有生成的時鐘采用單源引腳(多路選擇器輸出)。

局限性:

* 需要部署額外的時鐘門控檢查,時序變得至關(guān)重要。

可配置的基于多路選擇器的分頻器作為分?jǐn)?shù)時鐘分頻器使用

可配置的分?jǐn)?shù)時鐘分頻器或FCD是基于多路選擇器的分頻器中一個重要類別。分?jǐn)?shù)時鐘分頻器的重要特征包括:

* 這些分頻器是異步分頻器,分頻器的時鐘輸出與設(shè)計中生成的其他時鐘異步。

* 這些分頻器不具有50%的占空比。

* 輸出時鐘的最大頻率(fmax)(f /分頻系數(shù))四舍五入到.5或0

* 輸出時鐘的最小頻率(fmin)(f/分頻系數(shù))四舍五入到.5或0

所需的輸出頻率實際上是許多輸入時鐘周期中輸出時鐘的平均頻率。

FCD的概念

舉一個分?jǐn)?shù)時鐘分頻的例子,就可以理解FCD的概念。

假設(shè)時鐘分頻為1.3 - 這樣時鐘的最小頻率fmin= 1.5,最大頻率fmax= 1

也就是說:輸出時鐘的10個周期=輸入時鐘的13個周期

設(shè)最小頻率的輸出時鐘周期數(shù)為X

設(shè)最大頻率的輸出時鐘周期數(shù)為Y

因此

x + y = 10

1.5 x + Y = 13

由此我們解出

x = 6 y =4

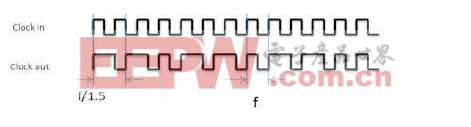

這樣,6×1.5=9個輸入時鐘周期,將除以1.5, 4個輸入時鐘周期將除以1。 1.3分頻的波形圖如下所示。這些分頻器常常用于逐級時鐘頻率切換,防止在瞬間出現(xiàn)高電流消耗(這可能導(dǎo)致晶體管的Vdd口出現(xiàn)異常電壓下降或上升,破壞設(shè)計,并可能引起芯片復(fù)位)。時鐘頻率的步長隨著設(shè)計中每單位時間允許的最大頻率增加或減少。

圖9:分?jǐn)?shù)時鐘分頻。

本文結(jié)論

本文向人們展示了目前大多數(shù)設(shè)計中都使用的基本可配置時鐘分頻器。盡管實施方案可能會有所不同,但是可配置分頻器的基本思路是一致的。由于每種時鐘分頻器各有優(yōu)點和局限性,設(shè)計人員在選擇時鐘分頻器類型時需要格外注意。雖然穿通時鐘方案使DFT時鐘更加簡單,其占空比局限性給時序團隊在分頻時鐘域關(guān)閉關(guān)鍵的半周期路徑時留下了繁瑣的工作。基于多路選擇器的分頻器提供50%占空比的輸出時鐘,但可能使DFT時鐘變得復(fù)雜。因此,如果在設(shè)計早期,從功能,DFT和時序方面詳細(xì)了解和分析時鐘的關(guān)鍵性因素,避免時鐘架構(gòu)變化,可能會在之后的時序收斂階段帶來意想不到的驚喜。

評論