Xilinx UltraScale?:為您未來架構(gòu)而打造的新一代架構(gòu)

Xilinx UltraScale™ 架構(gòu)針對要求最嚴苛的應(yīng)用,提供了前所未有的ASIC級的系統(tǒng)級集成和容量。

本文引用地址:http://www.104case.com/article/147542.htmUltraScale架構(gòu)是業(yè)界首次在All Programmable架構(gòu)中應(yīng)用最先進的ASIC架構(gòu)優(yōu)化。該架構(gòu)能從20nm平面FET結(jié)構(gòu)擴展至16nm鰭式FET晶體管技術(shù)甚至更高的技術(shù),同時還能從單芯片擴展到3D IC。借助Xilinx Vivado®設(shè)計套件的分析型協(xié)同優(yōu)化,UltraScale架構(gòu)可以提供海量數(shù)據(jù)的路由功能,同時還能智能地解決先進工藝節(jié)點上的頭號系統(tǒng)性能瓶頸。這種協(xié)同設(shè)計可以在不降低性能的前提下達到實現(xiàn)超過90%的利用率。

UltraScale架構(gòu)的突破包括:

• 幾乎可以在晶片的任何位置戰(zhàn)略性地布置類似于ASIC的系統(tǒng)時鐘,從而將時鐘歪斜降低達50%

• 系統(tǒng)架構(gòu)中有大量并行總線,無需再使用會造成時延的流水線,從而可提高系統(tǒng)速度和容量

• 甚至在要求資源利用率達到90%及以上的系統(tǒng)中,也能消除潛在的時序收斂問題和互連瓶頸

• 可憑借3D IC集成能力構(gòu)建更大型器件,并在工藝技術(shù)方面領(lǐng)先當(dāng)前行業(yè)標(biāo)準整整一代

• 能在更低的系統(tǒng)功耗預(yù)算范圍內(nèi)顯著提高系統(tǒng)性能,包括多Gb串行收發(fā)器、I/O以及存儲器帶寬

• 顯著增強DSP與包處理性能

賽靈思UltraScale架構(gòu)為超大容量解決方案設(shè)計人員開啟了一個全新的領(lǐng)域。

越多越好

自從“全面數(shù)字化”(all things digital)概念引入以來,“越多越好”成為了所有市場領(lǐng)域中數(shù)字系統(tǒng)的一種基本的、必然的發(fā)展趨勢。這一期望成為了促使系統(tǒng)要求更高分辨率、更高帶寬和更大存儲量的基本動力。而“更多”這一理念同時從邏輯上也引發(fā)了如下事實的產(chǎn)生:

•更多的器件生成更多數(shù)據(jù)。

• 更多的數(shù)據(jù)意味著數(shù)據(jù)必須更快流動。

• 更多快速流動的數(shù)據(jù)要求計算速度更快。

• 更多的應(yīng)用需要更快速地訪問更多數(shù)據(jù)。

• 數(shù)據(jù)量的增長和數(shù)據(jù)速率的提高對數(shù)據(jù)完整性提出了更高要求。

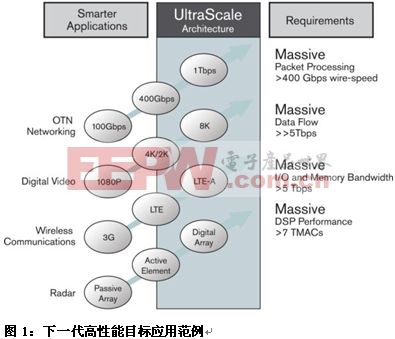

目前幾乎每個領(lǐng)域的數(shù)據(jù)創(chuàng)建和數(shù)據(jù)傳輸速率都在快速增長,這會加大對新型器件架構(gòu)的需求,以應(yīng)對如下問題所帶來的重重挑戰(zhàn):

•海量數(shù)據(jù)流以及類似于ASIC的時鐘布線

• 海量I/O和存儲器帶寬

• 更快的DSP和包處理

• 電源管理

• 多級安全

UltraScale架構(gòu):賽靈思的新一代All Programmable架構(gòu)

為了達到每秒數(shù)百Gb的系統(tǒng)性能和全線速下的智能處理能力,并擴展到Tb級和每秒萬億次浮點運算,需要采用一種新的架構(gòu)方案。為此,我們要做的不僅僅是簡單地提高每個晶體管或系統(tǒng)模塊的性能,或擴展系統(tǒng)中的模塊數(shù)量,而是要從根本上改善通信、時鐘、關(guān)鍵路徑和互連功能,以滿足海量數(shù)據(jù)流、實時數(shù)據(jù)包和圖像處理需求。

UltraScale™ 架構(gòu)通過在一個全面可編程(All Programmable)架構(gòu)中應(yīng)用最先進的ASIC 技術(shù),可應(yīng)對上述需要海量I/O和存儲器帶寬、海量數(shù)據(jù)流以及卓越DSP和包處理性能的挑戰(zhàn)。。UltraScale架構(gòu)經(jīng)過精調(diào)可提供大規(guī)模布線能力并且與Vivado®設(shè)計工具進行協(xié)同優(yōu)化,因此該架構(gòu)的利用率達到了空前的高水平(超過90%),而且不會降低性能。

UltraScale架構(gòu)是業(yè)界首次在All Programmable架構(gòu)中應(yīng)用最先進的ASIC架構(gòu)優(yōu)化該架構(gòu)能從20nm平面FET結(jié)構(gòu)擴展至16nm鰭式FET晶體管技術(shù)甚至更高的技術(shù),同時還能從單芯片擴展到3D IC。UltraScale架構(gòu)不僅能解決系統(tǒng)總吞吐量擴展和時延方面的局限性,而且還能直接應(yīng)對先進工藝節(jié)點上的頭號系統(tǒng)性能瓶頸,即互連問題。

Xilinx UltraScale架構(gòu)旨在滿足下一代系統(tǒng)級性能要求。(見圖1)

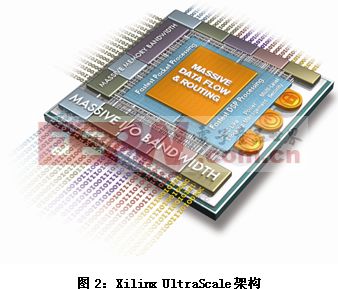

賽靈思對UltraScale架構(gòu)進行了數(shù)百項設(shè)計提升,并將這些改進實現(xiàn)有機結(jié)合,讓設(shè)計團隊能夠打造出比以往功能更強、運行速度更快、單位功耗性能更高的系統(tǒng)。見圖2。

存儲器相關(guān)文章:存儲器原理

評論