半導體制造:跟隨還是超越摩爾定律

1. 由于氮氧化硅(SiON)柵極介質厚度過薄難以控制,在降低柵極漏電和閾值變異性方面遇到挑戰。目前,各大芯片代工廠紛紛轉向新的材質和高K金屬柵極(HKMG)工藝技術(先柵極和后柵極工藝)。這一變化導致了必須在布線工具和設計規則檢查(DRC)工具中納入新的設計規則。

本文引用地址:http://www.104case.com/article/124079.htm2. 在193nm光刻基本限值下作業的挑戰。設計師必須加強對實施和簽核的光刻檢查。目前,各個領先的芯片代工廠均要求用戶在提交設計前實施某種形式的光刻檢查。比如,針對不同Foundry(代工廠)的特點,Synopsys提供不同的工具來協助識別和排除那些導致光刻問題和其它影響良率的設計。

3. 用于參數提取的新工藝拓撲結構建模方面的挑戰。目前,各大領先芯片代工廠正創建新的“通孔接觸”(via and contact)拓撲結構,來改善芯片的可制造性和維持其密度。STAR RC等提取工具已得到了更新,以更好地了解新的通孔蝕刻效應和凹刻接觸技術。

4. 管理參數異變性,尤其是在簽核期間異變性的挑戰。參數異變性,對比此前工藝節點中的狀況,其百分比相對基準數據已出現了顯著增長,不過利用最壞情況分析法又過于悲觀。目前,芯片代工廠和設計師開始要求采用高級片上變異(AOCV)設計和分析方法,來限定變異性和提供準時的簽核。同時要求EDA工具必須具備AOCV分析能力。

與此對應,22/20nm則有不同的要求,EDA工具面臨的主要挑戰包括以下4點。

1. 新限制性設計規則的增加,以確保利用193nm可成功實現絕對分辨率限值的光刻。為適應這些新規則的要求,必須對布局和布線工具以及DRC檢查進行升級。

2. 對于部分層級超越193nm光刻的限值方面的挑戰。包括通孔和金屬齒距在內的部分芯片層不能在單一光罩內進行投影成像,這是因為這些芯片層在20/22nm工藝下體積太小,密度太大,必須采取雙圖案模式,將一個單一芯片層的特性分離在兩個光罩內。雙圖案模式提出了新的間距要求,可能增加設計的面積。不過,智能化的布局和布線可以在實際實施時,緩解雙圖案模式對面積產生的絕大部分影響。

3. 新的提取需求——部分22/20nm工藝增加了凹刻接觸等新的結構和拓撲,要求必須具備新的提取能力。

4. 向鰭式場效晶體管(FINFET)/TriGate結構的演進——對整個半導體行業造成了重大影響的英特爾宣布,他們將轉向利用TriGate晶體管制造22nm芯片。FINFET/TriGate結構對提取和SPICE模擬具有更高的要求,Synopsys已經開始在EDA工具中考慮這些問題。同時,工藝和設備工程師要在FINFET上開展工藝或設備模擬,也必須擁有從二維TCAD轉向三維TCAD能力。

代工廠角度,陳家湘介紹,為了因應全新設計的挑戰,TSMC與fabless(無晶圓半導體)客戶應該更早、更深入及更緊密的合作,結合雙方的優勢共同因應未來在設計與技術上的挑戰。首先,foundry與fabless 應更早一步定位產品的設計;其次,雙方應該更深入地加強硅IP的合作,共同追求可制造性設計(DFM)與設計規范限制(RDR)等設計工具的一致性,進一步從設計到生產的過程中共同解決問題,提升產品質量。目前,TSMC 28nm設計生態環境已準備就緒,發表包括設計參考流程12.0版(Reference Flow 12.0)、模擬/混合訊號參考流程2.0版(Analog/Mixed Signal Reference Flow 2.0)等多項最新的定制化設計工具,強化既有的開放創新平臺設計生態環境,幫助客戶更快更好的開發28nm產品。另外,28nm產品已進入量產,客戶采用TSMC開放創新平臺(Open Innovation Platform)所規劃的28nm新產品設計定案(tape out)數量已經超過80個。

現實:成本逐漸成第一難題

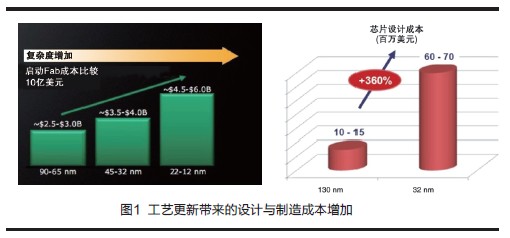

隨著半導體工藝向深亞微米發展,半導體設計與制造的成本都呈幾何級數增長,以設計為例,32nm的芯片設計成本比起130nm增長了360%,達到了6000萬美元,而制造的成本增加更為可怕,新建一條生產線從90nm的25億美元增加到22nm的超過45億美元(參見圖1)。因此,降低設計生產制造成本,逐漸成為采用先進制程的最大阻礙。

Jean-Marc Chery介紹,若想克服挑戰,設計層面最重要的是,技術研發人員與芯片設計、設計工具人員之間必須建立密切的合作關系。制造方面,意法半導體采用和制造技術開發者以及EDA公司緊密合作的方式,以降低自己采用新技術的成本支出,與國際半導體開發聯盟(ISDA)的合作就是其中一例。通過與出色的伙伴合作克服上述挑戰,為客戶提供最佳的解決方案,在成本增加有限的前提下不斷提高性能。即將到來的20nm技術節點將使28nm技術節點的系統芯片提高性能30%,并降低制造成本,我們將看到處理速度達到3 GHz的芯片,晶體管數量超過20億支的裸片,意法半導體將從2012年 (Q1,一季度)開始設計20nm芯片,從 2013 (Q1)年開始提供原型芯片。

漏電開關相關文章:漏電開關原理

評論