臺(tái)積電計(jì)劃2030年量產(chǎn)1nm,單個(gè)封裝可集成1萬(wàn)億個(gè)晶體管!

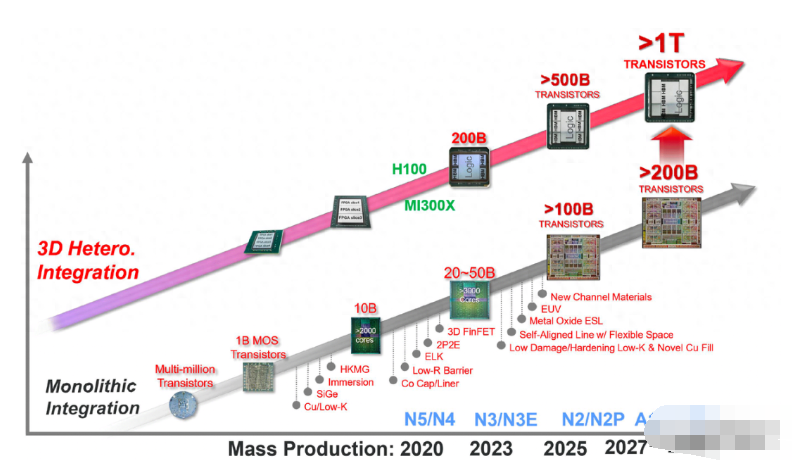

12月28日消息,據(jù)外媒tomshardware報(bào)道,晶圓代工大廠臺(tái)積電在IEDM大會(huì)上分享了其最新的Roadmap,計(jì)劃在2023年推出1nm級(jí)的A10制程,實(shí)現(xiàn)單個(gè)芯片上集成200億個(gè)晶體管,并依托于先進(jìn)封裝技術(shù),實(shí)現(xiàn)單個(gè)封裝上集成1萬(wàn)億個(gè)晶體管的目標(biāo)。

具體來(lái)說(shuō),根據(jù)臺(tái)積電的計(jì)劃,首先會(huì)在2025年量產(chǎn)2nm級(jí)的N2制程,2026年左右量產(chǎn)N2P制程,屆時(shí)將會(huì)采用新的通道材料、EUV、金屬氧化物ESL、自對(duì)齊線w / Flexible Space、低損傷/硬化Low-K & 新型銅填充等技術(shù),將實(shí)現(xiàn)單顆芯片集成超過(guò)1000億個(gè)晶體管,同時(shí)借助先進(jìn)的3D封裝技術(shù),實(shí)現(xiàn)單個(gè)封裝集成超過(guò)5000個(gè)晶體管。

在2027年之后,臺(tái)積電還將量產(chǎn)1.4nm級(jí)的A14制程,2030年將量產(chǎn)1nm級(jí)的A10制程,實(shí)現(xiàn)單芯片集成超過(guò)2000億個(gè)晶體管,借助3D封裝技術(shù),實(shí)現(xiàn)單個(gè)封裝內(nèi)集成超過(guò)1萬(wàn)億個(gè)晶體管。

雖然近年來(lái),摩爾定律的推進(jìn)持續(xù)放緩,但是臺(tái)積電深信,隨著2nm、1.4nm和1nm制程推出,未來(lái)五六年內(nèi),半導(dǎo)體芯片仍能在性能、功耗和晶體管密度進(jìn)一步提升。

目前市場(chǎng)上最復(fù)雜的單片處理器之一就是英偉達(dá)(Nvidia)的GH100,擁有800億個(gè)晶體管。臺(tái)積電表示,不久將出現(xiàn)更復(fù)雜的單晶片,晶體管數(shù)量將超過(guò)1000億個(gè),但制程上會(huì)越來(lái)越復(fù)雜,成本也會(huì)變高,因此許多公司會(huì)選擇多芯片封裝設(shè)計(jì),如AMD MI300X和英特爾Ponte Vecchio就由幾十個(gè)芯片組成。

編輯:芯智訊-浪客劍

*博客內(nèi)容為網(wǎng)友個(gè)人發(fā)布,僅代表博主個(gè)人觀點(diǎn),如有侵權(quán)請(qǐng)聯(lián)系工作人員刪除。