HBM的未來(lái):必要但昂貴

高帶寬內(nèi)存 (HBM) 正在成為超大規(guī)模廠商的首選內(nèi)存,但其在主流市場(chǎng)的最終命運(yùn)仍存在疑問。雖然它在數(shù)據(jù)中心中已經(jīng)很成熟,并且由于人工智能/機(jī)器學(xué)習(xí)的需求而使用量不斷增長(zhǎng),但其基本設(shè)計(jì)固有的缺陷阻礙了更廣泛的采用。一方面,HBM 提供緊湊的 2.5D 外形尺寸,可大幅減少延遲。

Rambus產(chǎn)品營(yíng)銷高級(jí)總監(jiān) Frank Ferro在本周的 Rambus 設(shè)計(jì)峰會(huì)上的演講中表示:“HBM 的優(yōu)點(diǎn)在于,您可以在很小的占地面積內(nèi)獲得所有這些帶寬,而且還可以獲得非常好的電源效率。”

缺點(diǎn)是它依賴昂貴的硅中介層和 TSV 來(lái)運(yùn)行。

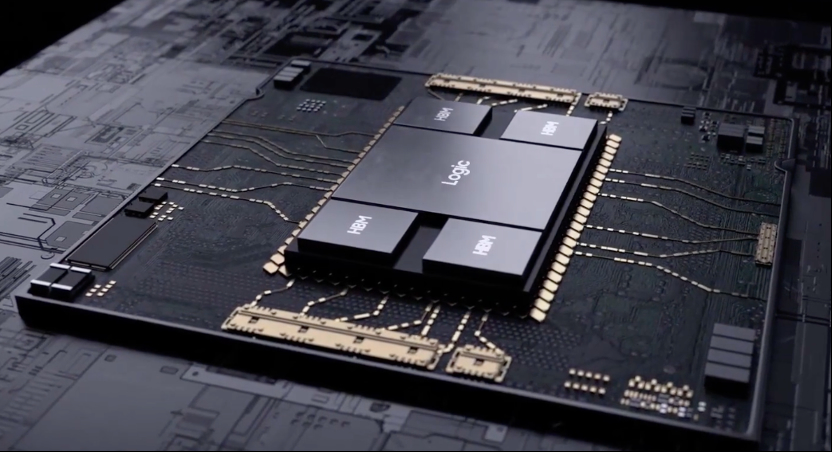

圖 1:實(shí)現(xiàn)最大數(shù)據(jù)吞吐量的 HBM 堆棧

Cadence IP 團(tuán)隊(duì)產(chǎn)品營(yíng)銷總監(jiān) Marc Greenberg 表示:“目前困擾高帶寬內(nèi)存的問題之一是成本。3D 堆疊成本高昂。有一個(gè)邏輯芯片位于芯片堆疊的底部,這是您必須支付的額外硅片。然后是硅中介層,它位于 CPU 或 GPU 以及 HBM 內(nèi)存下的所有內(nèi)容之下。然后,你需要一個(gè)更大的封裝等等,這是需要昂貴的代價(jià)的。”Marc Greenberg進(jìn)一步指出:“目前存在的 HBM 脫離了消費(fèi)者領(lǐng)域,并更牢固地放置在服務(wù)器機(jī)房或數(shù)據(jù)中心,存在許多系統(tǒng)成本。相比之下,GDDR6 等圖形內(nèi)存雖然無(wú)法提供與 HBM 一樣多的性能,但成本卻顯著降低。GDDR6 的單位成本性能實(shí)際上比 HBM 好得多,但 GDDR6 器件的最大帶寬與 HBM 的最大帶寬不匹配。”

Greenberg 表示,這些差異為公司選擇 HBM 提供了令人信服的理由,即使它可能不是他們的第一選擇。“HBM 提供了大量的帶寬,并且點(diǎn)對(duì)點(diǎn)傳輸?shù)哪芰繕O低。您使用 HBM 是因?yàn)槟仨氝@樣做,因?yàn)槟鷽]有其他解決方案可以為您提供所需的帶寬或所需的功率配置文件。”

而且 HBM 只會(huì)變得越來(lái)越快。“我們預(yù)計(jì) HBM3 Gen2 的帶寬將提高 50%,”美光計(jì)算產(chǎn)品事業(yè)部副總裁兼總經(jīng)理 Praveen Vaidyanathan 說(shuō)道。“從美光的角度來(lái)看,我們預(yù)計(jì) HBM3 Gen2 產(chǎn)品將在 2024 財(cái)年期間實(shí)現(xiàn)量產(chǎn)。在 2024 日歷年年初,我們預(yù)計(jì)隨著時(shí)間的推移,將開始為預(yù)期的數(shù)億美元收入機(jī)會(huì)做出貢獻(xiàn)。此外,我們預(yù)測(cè)美光的 HBM3 將貢獻(xiàn)比 DRAM 更高的利潤(rùn)。”

盡管如此,經(jīng)濟(jì)因素可能會(huì)迫使許多設(shè)計(jì)團(tuán)隊(duì)考慮價(jià)格敏感應(yīng)用的替代方案。

“如果有任何其他方法可以將問題細(xì)分為更小的部分,您可能會(huì)發(fā)現(xiàn)它更具成本效益,”Greenberg 指出。“例如,與其面對(duì)一個(gè)巨大的問題并說(shuō),‘我必須在一個(gè)硬件上執(zhí)行所有這些操作,而且我必須在那里擁有 HBM,也許我可以將其分成兩部分,讓兩個(gè)進(jìn)程并行運(yùn)行,也許連接到 DDR6。如果我能夠?qū)⒃搯栴}細(xì)分為更小的部分,那么我可能會(huì)以更低的成本完成相同數(shù)量的計(jì)算。但如果您需要那么大的帶寬,那么 HBM 就是您可以承受成本的方法。”

散熱挑戰(zhàn)

另一個(gè)主要缺點(diǎn)是 HBM 的 2.5D 結(jié)構(gòu)會(huì)積聚熱量,而其放置在靠近 CPU 和 GPU 的位置會(huì)加劇這種情況。事實(shí)上,在試圖給出不良設(shè)計(jì)的理論示例時(shí),很難想出比當(dāng)前布局更糟糕的東西,當(dāng)前布局將 HBM及其熱敏 DRAM 堆棧放置在計(jì)算密集型熱源附近。

“最大的挑戰(zhàn)是熱量,”Greenberg 說(shuō)。“你有一個(gè) CPU,根據(jù)定義它會(huì)生成大量數(shù)據(jù)。您通過此接口每秒傳輸太比特?cái)?shù)。即使每筆交易只有少量皮焦耳,但每秒都會(huì)執(zhí)行十億筆交易,因此您的 CPU 會(huì)非常熱。它不僅僅是移動(dòng)周圍的數(shù)據(jù)。它也必須進(jìn)行計(jì)算。最重要的是最不喜歡熱的半導(dǎo)體組件,即 DRAM。85℃左右它開始忘記東西,125℃左右則完全心不在焉。這是兩個(gè)截然不同的事情。”

還有一個(gè)可取之處。“擁有 2.5D 堆棧的優(yōu)勢(shì)在于,CPU 很熱,而 HBM 位于 CPU 旁邊,因此喜歡冷,之間有一定的物理隔離,”他說(shuō)。

在延遲和熱量之間的權(quán)衡中,延遲是不可變的。“我沒有看到任何人犧牲延遲,”Synopsys 內(nèi)存接口 IP 解決方案產(chǎn)品線總監(jiān) Brett Murdock說(shuō)道。“我看到他們推動(dòng)物理團(tuán)隊(duì)尋找更好的冷卻方式,或者更好的放置方式,以保持較低的延遲。”

考慮到這一挑戰(zhàn),多物理場(chǎng)建模可以提出減少熱問題的方法,但會(huì)產(chǎn)生相關(guān)成本。“這就是物理學(xué)變得非常困難的地方,” Ansys產(chǎn)品經(jīng)理 Marc Swinnen 說(shuō)。“功率可能是集成所能實(shí)現(xiàn)的最大限制因素。任何人都可以設(shè)計(jì)一堆芯片并將它們?nèi)窟B接起來(lái),所有這些都可以完美工作,但你無(wú)法冷卻它。散發(fā)熱量是可實(shí)現(xiàn)目標(biāo)的根本限制。”

潛在的緩解措施可能很快就會(huì)變得昂貴,從微流體通道到浸入非導(dǎo)電液體,再到確定散熱器上需要多少個(gè)風(fēng)扇或翅片,以及是否使用銅或鋁。

可能永遠(yuǎn)不會(huì)有完美的答案,但模型和對(duì)期望結(jié)果的清晰理解可以幫助創(chuàng)建合理的解決方案。“你必須定義最佳對(duì)你來(lái)說(shuō)意味著什么,”Swinnen說(shuō)。“你想要最好的熱量嗎?最好的成本??jī)烧咧g的最佳平衡?你將如何衡量它們?答案依賴于模型來(lái)了解物理學(xué)中實(shí)際發(fā)生的情況。它依靠人工智能來(lái)處理這種復(fù)雜性并創(chuàng)建元模型來(lái)捕捉這個(gè)特定優(yōu)化問題的本質(zhì),并快速探索這個(gè)廣闊的空間。”

HBM 和 AI

雖然很容易想象計(jì)算是 AI/ML 最密集的部分,但如果沒有良好的內(nèi)存架構(gòu),這一切都不會(huì)發(fā)生。需要內(nèi)存來(lái)存儲(chǔ)和檢索數(shù)萬(wàn)億次計(jì)算。事實(shí)上,在某種程度上,添加更多 CPU 并不會(huì)提高系統(tǒng)性能,因?yàn)閮?nèi)存帶寬無(wú)法支持它們。這就是臭名昭著的“內(nèi)存墻”瓶頸。

Quadric首席營(yíng)銷官 Steve Roddy 表示,從最廣泛的定義來(lái)看,機(jī)器學(xué)習(xí)只是曲線擬合。“在訓(xùn)練運(yùn)行的每次迭代中,你都在努力越來(lái)越接近曲線的最佳擬合。這是一個(gè) X,Y 圖,就像高中幾何一樣。大型語(yǔ)言模型基本上是同一件事,但是是 100 億維,而不是 2 維。”

因此,計(jì)算相對(duì)簡(jiǎn)單,但內(nèi)存架構(gòu)可能令人難以置信。

Roddy 解釋說(shuō):“其中一些模型擁有 1000 億字節(jié)的數(shù)據(jù),對(duì)于每次重新訓(xùn)練迭代,您都必須通過數(shù)據(jù)中心的背板從磁盤上取出 1000 億字節(jié)的數(shù)據(jù)并放入計(jì)算箱中。”“在兩個(gè)月的訓(xùn)練過程中,你必須將這組巨大的內(nèi)存值來(lái)回移動(dòng)數(shù)百萬(wàn)次。限制因素是數(shù)據(jù)的移入和移出,這就是為什么人們對(duì) HBM 或光學(xué)互連等從內(nèi)存?zhèn)鬏數(shù)接?jì)算結(jié)構(gòu)的東西感興趣。所有這些都是人們投入數(shù)十億美元風(fēng)險(xiǎn)投資的地方,因?yàn)槿绻隳芸s短距離或時(shí)間,你就可以大大簡(jiǎn)化和縮短訓(xùn)練過程,無(wú)論是切斷電源還是加快訓(xùn)練速度。”

出于所有這些原因,高帶寬內(nèi)存被認(rèn)為是 AI/ML 的首選內(nèi)存。“它為您提供了某些訓(xùn)練算法所需的最大帶寬,”Rambus 的 Ferro 說(shuō)。“從你可以擁有多個(gè)內(nèi)存堆棧的角度來(lái)看,它是可配置的,這為你提供了非常高的帶寬。”

這就是人們對(duì) HBM 如此感興趣的原因。“我們的大多數(shù)客戶都是人工智能客戶,”Synopsys 的Murdock說(shuō)。“他們正在 LPDDR5X 接口和 HBM 接口之間進(jìn)行一項(xiàng)重大的基本權(quán)衡。唯一阻礙他們的是成本。他們真的很想去 HBM。這是他們對(duì)技術(shù)的渴望,因?yàn)槟銦o(wú)法觸及在一個(gè) SoC 周圍可以創(chuàng)建的帶寬量。現(xiàn)在,我們看到 SoC 周圍放置了 6 個(gè) HBM 堆棧,這需要大量的帶寬。”

然而,人工智能的需求如此之高,以至于 HBM 減少延遲的前沿特征突然顯得過時(shí)且不足。這反過來(lái)又推動(dòng)了下一代 HBM 的發(fā)展。

“延遲正在成為一個(gè)真正的問題,”Ferro說(shuō)。“在 HBM 的前兩輪中,我沒有聽到任何人抱怨延遲。現(xiàn)在我們一直收到有關(guān)延遲的問題。”

Ferro 建議,鑒于當(dāng)前的限制,了解數(shù)據(jù)尤為重要。“它可能是連續(xù)的數(shù)據(jù),例如視頻或語(yǔ)音識(shí)別。它可能是事務(wù)性的,就像財(cái)務(wù)數(shù)據(jù)一樣,可能非常隨機(jī)。如果您知道數(shù)據(jù)是隨機(jī)的,那么設(shè)置內(nèi)存接口的方式將與流式傳輸視頻不同。這些是基本問題,但也有更深層次的問題。我要在記憶中使用的字長(zhǎng)是多少??jī)?nèi)存的塊大小是多少?您對(duì)此了解得越多,您設(shè)計(jì)系統(tǒng)的效率就越高。如果您了解它,那么您可以定制處理器以最大限度地提高計(jì)算能力和內(nèi)存帶寬。我們看到越來(lái)越多的 ASIC 式 SoC 正在瞄準(zhǔn)特定市場(chǎng)細(xì)分市場(chǎng),以實(shí)現(xiàn)更高效的處理。”

使其更便宜(也許)

如果經(jīng)典的 HBM 實(shí)現(xiàn)是使用硅中介層,那么就有希望找到成本更低的解決方案。“還有一些方法可以在標(biāo)準(zhǔn)封裝中嵌入一小塊硅,這樣就沒有一個(gè)完整的硅中介層延伸到所有東西下面,”Greenberg說(shuō)。“CPU 和 HBM 之間只有一座橋梁。此外,在標(biāo)準(zhǔn)封裝技術(shù)上允許更細(xì)的引腳間距也取得了進(jìn)展,這將顯著降低成本。還有一些專有的解決方案,人們?cè)噲D通過高速 SerDes 類型連接來(lái)連接存儲(chǔ)器,沿著 UCIE 的路線,并可能通過這些連接來(lái)連接存儲(chǔ)器。目前,這些解決方案是專有的,但我希望它們能夠標(biāo)準(zhǔn)化。”

Greenberg表示,可能存在平行的發(fā)展軌跡:“硅中介層確實(shí)提供了可能的最精細(xì)的引腳間距或線間距——基本上是用最少的能量實(shí)現(xiàn)最大的帶寬——所以硅中介層將永遠(yuǎn)存在。但如果我們作為一個(gè)行業(yè)能夠聚集在一起并決定一個(gè)適用于標(biāo)準(zhǔn)封裝的內(nèi)存標(biāo)準(zhǔn),那么就有可能提供類似的帶寬,但成本卻要低得多。”

人們正在不斷嘗試降低下一代的成本。“臺(tái)積電已宣布他們擁有三種不同類型的中介層,”Ferro 說(shuō)。“他們有一個(gè) RDL 中介層,他們有硅中介層,他們有一些看起來(lái)有點(diǎn)像兩者的混合體。還有其他技術(shù),例如如何完全擺脫中介層。您可能會(huì)在接下來(lái)的 12 或 18 個(gè)月內(nèi)看到一些如何在頂部堆疊 3D 內(nèi)存的原型,理論上可以擺脫中介層。事實(shí)上,IBM 多年來(lái)一直在這樣做,但現(xiàn)在已經(jīng)到了你不必成為 IBM 也能做到這一點(diǎn)的地步。”

解決該問題的另一種方法是使用較便宜的材料。“正在研究非常細(xì)間距的有機(jī)材料,以及它們是否足夠小以處理所有這些痕跡,”Ferro說(shuō)。“此外,UCIe是通過更標(biāo)準(zhǔn)的材料連接芯片的另一種方式,以節(jié)省成本。但同樣,你仍然必須解決通過這些基材的數(shù)千條痕跡的問題。”

Murdock希望通過規(guī)模經(jīng)濟(jì)來(lái)削減成本。“隨著 HBM 越來(lái)越受歡迎,成本方面將有所緩解。HBM 與任何 DRAM 一樣,歸根結(jié)底都是一個(gè)商品市場(chǎng)。在中介層方面,我認(rèn)為下降速度不會(huì)那么快。這仍然是一個(gè)需要克服的挑戰(zhàn)。”

但原材料成本并不是唯一的考慮因素。“這還取決于 SoC 需要多少帶寬,以及電路板空間等其他成本,”Murdock 說(shuō)。“對(duì)于那些想要高速接口并需要大量帶寬的人來(lái)說(shuō),LPDDR5X 是一種非常受歡迎的替代方案,但與 HBM 堆棧的通道數(shù)量相匹配所需的 LPDDR5X 通道數(shù)量相當(dāng)大。您有大量的設(shè)備成本和電路板空間成本,這些成本可能令人望而卻步。僅就美元而言,也可能是一些物理限制促使人們轉(zhuǎn)向 HBM,盡管從美元角度來(lái)看它更昂貴。”

其他人對(duì)未來(lái)成本削減則不太確定。Objective Analysis 首席分析師 Jim Handy 表示:“降低 HBM 成本將是一項(xiàng)挑戰(zhàn)。”“由于將 TSV 放置在晶圓上的成本很高,因此加工成本已經(jīng)明顯高于標(biāo)準(zhǔn) DRAM。這使得它無(wú)法擁有像標(biāo)準(zhǔn) DRAM 一樣大的市場(chǎng)。由于市場(chǎng)較小,規(guī)模經(jīng)濟(jì)導(dǎo)致成本在一個(gè)自給自足的過程中更高。體積越小,成本越高,但成本越高,使用的體積就越少。沒有簡(jiǎn)單的方法可以解決這個(gè)問題。”

盡管如此,Handy 對(duì) HBM 的未來(lái)持樂觀態(tài)度,并指出與 SRAM 相比,它仍然表現(xiàn)出色。“HBM 已經(jīng)是一個(gè)成熟的 JEDEC 標(biāo)準(zhǔn)產(chǎn)品,”他說(shuō)。“這是一種獨(dú)特的 DRAM 技術(shù)形式,能夠以比 SRAM 低得多的成本提供極高的帶寬。它還可以通過封裝提供比 SRAM 更高的密度。它會(huì)隨著時(shí)間的推移而改進(jìn),就像 DRAM 一樣。隨著接口的成熟,預(yù)計(jì)會(huì)看到更多巧妙的技巧來(lái)提高其速度。”

事實(shí)上,盡管面臨所有挑戰(zhàn),HBM 還是有理由保持樂觀。“標(biāo)準(zhǔn)正在迅速發(fā)展,”費(fèi)羅補(bǔ)充道。“如果你看看 HBM 如今的發(fā)展,你會(huì)發(fā)現(xiàn)它大約以兩年為節(jié)奏,這確實(shí)是一個(gè)驚人的速度。”

來(lái)源:半導(dǎo)體行業(yè)觀察

*博客內(nèi)容為網(wǎng)友個(gè)人發(fā)布,僅代表博主個(gè)人觀點(diǎn),如有侵權(quán)請(qǐng)聯(lián)系工作人員刪除。