vhdl-ams 文章 最新資訊

Xilinx進(jìn)駐北京新址并宣布成立中國研發(fā)中心

- 全球可編程平臺領(lǐng)導(dǎo)廠商賽靈思公司?(Xilinx,?Inc.)日前在進(jìn)駐北京新址的慶典上,強(qiáng)調(diào)其對高增長的中國市場的承諾。該公司不斷擴(kuò)大其在亞太地區(qū)的影響力,包括開設(shè)研發(fā)中心,并將本地銷售、市場營銷和應(yīng)用工程設(shè)計等業(yè)務(wù)整合到統(tǒng)一的辦公地點。新址面積達(dá)?2,000?平米,將為北京本地、整個亞太區(qū)乃至跨國客戶提供強(qiáng)有力的支持。 從左至右,?北京化工大學(xué)教授何賓,?賽靈思軟件研發(fā)總監(jiān)宋傳華博士,?全球研發(fā)高級總監(jiān)Devadas,&nbs

- 關(guān)鍵字: Xilinx 可編程平臺 FPGA,(AMS

基于FPGA的數(shù)字濾波器設(shè)計

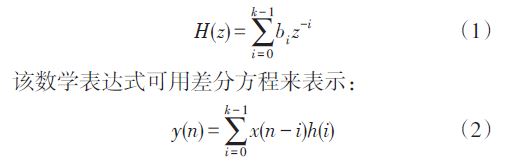

- 利用VHDL語言設(shè)計數(shù)字濾波器,主要在于如何實現(xiàn)乘法。乘法常用的實現(xiàn)方法有位串行乘法、分布式算法和并行乘法等。位串行乘法能節(jié)省大量硬件資源,但運算周期過長,對于數(shù)字濾波器這種高速率要求不宜采取。分布式算法是現(xiàn)在比較流行的一種乘法實現(xiàn)方式,所用硬件資源較少,運算速率也較快,但這只是針對小位寬乘法來說。對于數(shù)字濾波器的較大位寬的乘法,不宜采取。并行乘法,算法實現(xiàn)簡單直觀,對于現(xiàn)在資源豐富的FPGA,很好實現(xiàn)

- 關(guān)鍵字: 濾波器 數(shù)字 FPGA VHDL

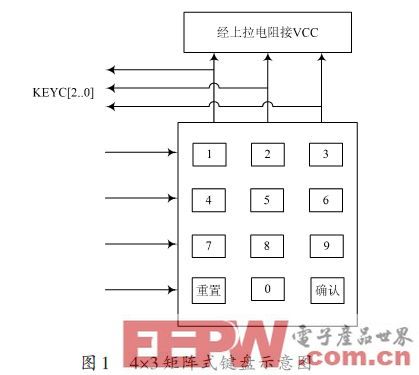

基于FPGA的多功能電子密碼鎖設(shè)計

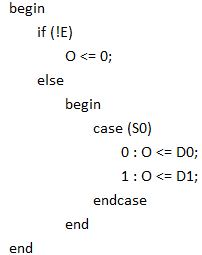

- 0 引言 傳統(tǒng)機(jī)械鎖的防盜功能差,在現(xiàn)代高科技安防系統(tǒng)中無法起到作用,已逐步被更可靠、更智能的電子數(shù)字密碼鎖代替。目前市場上的大部分密碼鎖產(chǎn)品是以單片機(jī)為核心的,利用軟件進(jìn)行控制,實際應(yīng)用中系統(tǒng)穩(wěn)定性較差且成本高。本文研究的是電子密碼鎖的一種純硬件實現(xiàn)方案,為彌補(bǔ)傳統(tǒng)技術(shù)的不足,采用EDA技術(shù)在可編程芯片上實現(xiàn)密碼的存儲、運算等操作,使產(chǎn)品既具有硬件的安全性和高速性,又具有軟件開發(fā)的靈活性和易維護(hù)性。 1 主要技術(shù)與開發(fā)環(huán)境 1.1 EDA技術(shù)及特點 EDA(Electronic Design A

- 關(guān)鍵字: FPGA VHDL

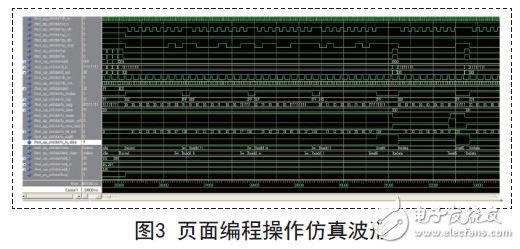

基于FPGA的ARM并行總線設(shè)計與仿真分析

- 在數(shù)字系統(tǒng)的設(shè)計中,F(xiàn)PGA+ARM的系統(tǒng)架構(gòu)得到了越來越廣泛的應(yīng)用,F(xiàn)PGA主要實現(xiàn)高速數(shù)據(jù)的處理;ARM主要實現(xiàn)系統(tǒng)的流程控制。人機(jī)交互。外部通信以及FPGA控制等功能。I2C、SPI等串行總線接口只能實現(xiàn)FPGA和ARM之間的低速通信; 當(dāng)傳輸?shù)臄?shù)據(jù)量較大。要求高速傳輸時,就需要用并行總線來進(jìn)行兩者之間的高速數(shù)據(jù)傳輸。

- 關(guān)鍵字: FPGA ARM DATA VHDL 數(shù)據(jù)總線

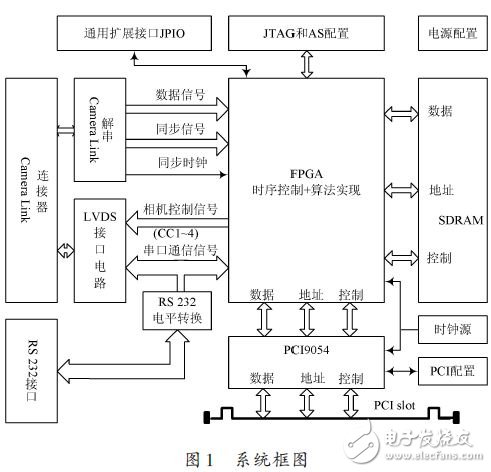

基于FPGA的采集卡的圖像增強(qiáng)算法應(yīng)用研究

- 圖像在采集過程中不可避免地會受到傳感器靈敏度、噪聲干擾以及模數(shù)轉(zhuǎn)化時量化問題等因素影響而導(dǎo)致圖像無法達(dá)到人眼的視覺效果,為了實現(xiàn)人眼觀察或者機(jī)器自動分析的目的,對原始圖像所做的改善行為,就被稱作圖像增強(qiáng)技術(shù)。

- 關(guān)鍵字: 傳感器 圖像增強(qiáng) FPGA PCI VHDL

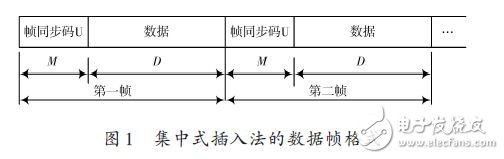

基于VHDL的QPSK調(diào)制解調(diào)系統(tǒng)設(shè)計與仿真

- 文中詳細(xì)介紹了QPSK技術(shù)的工作原理和QPSK調(diào)制、解調(diào)的系統(tǒng)設(shè)計方案,并通過VHDL語言編寫調(diào)制解調(diào)程序和QuaitusII軟件建模對程序進(jìn)行仿真,通過引腳鎖定,下載程序到FPGA芯片EP1K30TC144-3中驗證。軟件仿真和硬件驗證結(jié)果表明了該設(shè)計的正確性和可行性,由于采用FPGA芯片,減小了硬件設(shè)計的復(fù)雜性,該設(shè)計具有便于移植維護(hù)和升級的特點。

- 關(guān)鍵字: VHDL QPSK 調(diào)制解調(diào)系統(tǒng) 設(shè)計與仿真

vhdl-ams介紹

即IEEE 1076.1標(biāo)準(zhǔn)。

VHDL-AMS是VHDL的一個分支,它支持模擬、數(shù)字、數(shù)模混合電路系統(tǒng)的建模與仿真。

http://www.eda.org/vhdl-ams/

Verilog-AMS與之類似。支持模擬、數(shù)字、數(shù)模混合電路系統(tǒng)的建模與仿真。

http://www.eda.org/verilog-ams/

The VHDL-AMS language [ 查看詳細(xì) ]

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司