基于FPGA的UART 16倍頻采樣的VHDL設計

概述

本文引用地址:http://www.104case.com/article/189636.htm隨著電子設計自動化(EDA)技術的發展,可編程邏輯器件FPGA/CPLD已經在許多方面得到了廣泛應用,而UART(通用異步收發器) 是在數字通信和控制系統中廣泛使用的串行數據傳輸協議。因此越來越多用戶根據自己的需要,以EDA技術作為開發手段,用一塊FPGA/CPLD設計出符合自己需要的UART芯片。基于FPGA/ CPLD的UART設計在諸多文獻中都有論述,在此不再對UART整個功能模塊實現做太多的論述。本文著重分析UART接收器起始位的檢測。

3倍頻采樣的缺陷

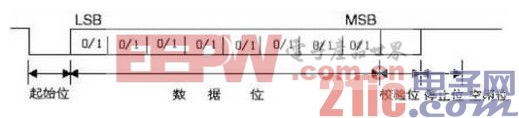

首先,串行異步通信規定了字符數據的傳送格式。每一幀數據由起始位、數據位、奇偶校驗位、停止位和線路空閑狀態組成,格式如圖1所示。一般情況起始位為1位,數據位為5、6、7或8位、奇偶校驗位為1位,停止位為1、1.5或2位。其中的起始位和停止位就是用來實現字符的同步。在空閑狀態,傳送線為邏輯“1”狀態。數據的傳送總是以一個“起始位”開始的,接著是要傳送的若干數據位,低位先行,最后是一個“1”狀態的“停止位”;那么,當接收器檢測到一個“1”向“0”的跳變時,便視為可能的起始位。起始位被確認后,就知道發送器已開始發送,當接收了已協議好的位數后并接收到字符幀中停止位就是一幀字符數據已發送完畢。這樣,接收器就知道發送器何時開始發送數據和何時結束發送數據。

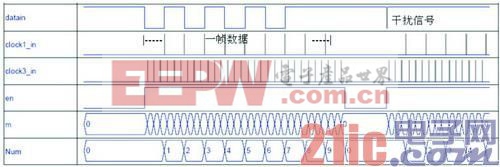

要提高接收器的接收準確性,減少誤碼率,必須要用比數據波特率高n 倍(n≥1)的速率對數據進行采樣。文獻2中采用了非常規的3倍頻采樣方法:用3倍頻的波特率對每一位數據進行采樣(如圖2所示),然后對3次采樣結果進行判決。如果3次采樣中至少有2次為高電平,則接收這一位數據被判決為高電平,否則,為低電平。

此方法剛開始給人感覺比常規的16倍頻采樣準確性高,因為每一位數據都進行3取2的判決,而16倍頻采樣對每位數據只進行一次中間采樣。然而筆者在實際應用中發現了其存在抗干擾性差,移植性差等不足。筆者在應用中自定義的異步數據幀長達21位,應用環境是渦輪工作間。在這樣條件下,3倍頻采樣比在良好的實驗室環境性能差了很多,誤碼率很高。

經分析代碼,發現3倍頻采樣方法在檢測異步數據起始位沒有任何的抗干擾處理。如果在接收線上存在干擾信號,即使是一個很窄負脈沖干擾,接收器也會誤判為是數據幀的起始位,從而產生采樣時鐘進行后續的數據采樣。圖3所示為存在干擾信號時,檢測起始位信號時序仿真波形。圖中COLCK3-IN是3倍頻采樣時鐘,CLOCK1-IN是數據波特率,DATAIN是接收線上的數據。從圖中看出,干擾信號后,COLCK3-IN時鐘產生,接收器接收數據。可見接收到的數據都是錯誤數據。簡單說,文獻2中所論述方法不能識別真假數據起始位。再從程序可移植性來說,3倍頻采樣時鐘是用三個數值進行計數判斷而得,當波特率改變,其數值都要做相應改變,這就增加了程序的修改難度。

16倍頻采樣起始位的檢測

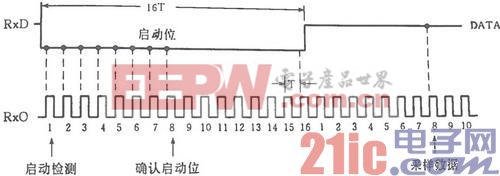

3倍頻采樣方法無法識別真假數據起始位,導致其抗干擾性差,準確性得不到保證。筆者拋棄非常規3倍頻采樣方法,采用了常規的16倍頻采樣方法:采用數據速率的16倍進行采樣,采樣時鐘連續采樣到8個低電平信號,可確定該低電平為真正的起始位,從而防止干擾信號產生的假起始位現象的發生。此后,接收器每隔16個采樣時鐘采樣一次,并把采樣到的數據作為輸入數據,以移位方式存入到接收移位寄存器。

fpga相關文章:fpga是什么

評論