基于FPGA的IRIG-B標準DC code編碼器VHDL設計

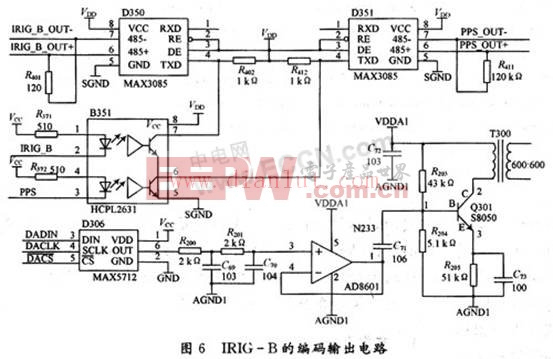

摘要:為了實現靶場時統終端輸出IRIG-B標準DC code信號,采用VHDL語言在FPGA邏輯電路中設計了DC code編碼器硬件電路,通過QuartusⅡ軟件建立工程文件對VHDL語言DC code編碼器電路進行編譯和仿真,獲得了符合IRIG-B標準的DC code信號。經過實踐驗證,該電路具有實現方法簡單、電路穩定性好、精度高的特點,實測同步精度小于1μs。

關鍵詞:IRIG-B;DC code;FPGA;VHDL

O 引言

在測控設備的時間統一系統向靶場試驗系統提供標準時間和頻率信號,以實現整個試驗系統的時間和頻率的統一,是由各種電子設備組成的一套完整系統。時統設備閣向用戶設備發送的時間信號中,含有時間信息編碼的串行時間碼,該碼應與標準時間精確同步的時間信號,適用于信道傳輸。IRIG(Inter Range Instrumentation Group)是美國RCC(Range Commanders Council)所屬的負責制定靶場標準等工作的機構,由其所屬TCG負責,制定了靶場時統和通信系統的標準。IRIG時間標準包括并行時間碼格式和串行時間碼格式,IRIG-B碼是串行時間碼格式,是我國標準化時統設備與用戶設備接口的時間信號標準的基礎。

1 IRIG-B標準DC碼

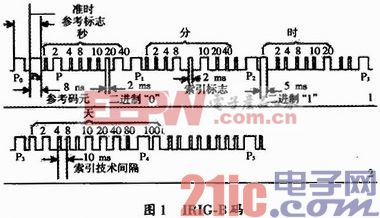

IRIG-B碼的幀頻是1幀/s,每一幀包括100個碼元(脈沖),每個碼元的準時參考點是該脈沖的前沿。IRIG-B碼采用脈寬調制的方法表示,碼元的脈沖寬度有3種,每種脈寬代表各自不同的信息,分別為脈寬2 ms代表二進制“0”、脈寬5 ms代表二進制“1”、脈寬8 ms代表該碼元為標識位。一幀IRIG-B由100個碼元組成,從參考碼元PR開始到位置識別標志P0結束。參考標志是由位置識別標志P0和相鄰的參考碼元PR組成的,PR的前沿即為該幀B碼的準秒時刻。在一幀B碼中,每10個碼元中有一個位置標示符,被記作P1,P2,P3,…,P9,P0。如圖1所示。

每幀中表示時間信息的碼元共有30個,時間信息采用二-十進制編碼,它所表達的時間包括:從00~59共7個碼元的‘秒’信息、從00~59共7個碼元的‘分’信息、從00~23共6個碼元的‘時’信息、從001~365或366共10位碼元的‘天’信息。幀中還有特標控制等信息。所有未攜帶信息的碼元其寬度均為2 ms。

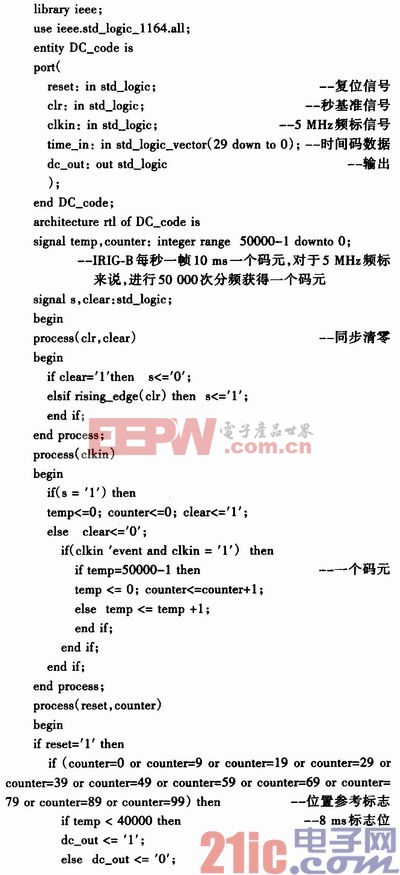

2 VHDL語言實現

VHDL語言實現程序如下:

fpga相關文章:fpga是什么

脈寬調制相關文章:脈寬調制原理

評論