- 1. 實驗目的(1)熟悉和掌握FPGA開發流程和Lattice Diamond軟件使用方法;(2)通過實驗理解和掌握數碼管驅動;(3)學習用Verilog HDL描述數碼管驅動電路。2. 實驗任務在數碼管上顯示數字。3. 實驗原理數碼管是工程設計中使用很廣的一種顯示輸出器件。一個7段數碼管(如果包括右下的小點可以認為是8段)分別由a、b、c、d、e、f、g位段和表示小數點的dp位段組成。實際是由8個LED燈組成的,控制每個LED的點亮或熄滅實現數字顯示。通常數碼管分為共陽極數碼管和共陰極數碼管,結構如下圖

- 關鍵字:

七段數碼管 FPGA Lattice Diamond Verilog HDL

- 當前最流行的硬件設計語言有兩種,即 VHDL 與 Verilog HDL,兩者各有優劣,也各有相當多的擁護者。VHDL 語言由美國軍方所推出,最早通過國際電機工程師學會(IEEE)的標準,在北美及歐洲應用非常普遍。而 Verilog HDL 語言則由 Gateway 公司提出,這家公司輾轉被Cadence所購并,并得到Synopsys的支持。在得到這兩大 EDA 公司的支持后,也隨后通過了 IEEE 標準,在美國、日本及中國臺灣地區使用非常普遍。 我們把這兩種語言具體比較下: 1.整體結構 點評

- 關鍵字:

VHDL Verilog

- 介紹了H.264的量化算法,并用Modelsim進行了仿真,結果與理論完全一致。分析了在FPGA開發板上的資源的消耗。由此可知,完全可以用FPGA實現H.264的量化

- 關鍵字:

Verilog 264 AVC

- 本章介紹Verilog HDL的基本要素,包括標識符、注釋、數值、編譯程序指令、系統任務和系統函數。另外,本章還介紹了Verilog硬件描述語言中的兩種數據類

- 關鍵字:

Verilog FPGA

- 1 功能概述流水廣告燈主要應用于LED燈光控制。通過程序控制LED的亮和滅, 多個LED燈組成一個陣列,依次逐個點亮的時候像流水一樣,所以叫流水燈。由于

- 關鍵字:

流水燈 Verilog fpga

- 大學時代第一次接觸FPGA至今已有10多年的時間,至今記得當初第一次在EDA實驗平臺上完成數字秒表、搶答器、密碼鎖等實驗時那個興奮勁。當時由于沒有接觸到HDL硬件描述語言,設計都是在MAX+plus II原理圖環境下用74系列邏輯器件搭建起來的。

后來讀研究生,工作陸陸續續也用過Quartus II、FoundaTIon、ISE、Libero,并且學習了verilogHDL語言,學習的過程中也慢慢體會到verilog的妙用,原來一小段語言就能完成復雜的原理圖設計,而且語言的移植性可操作性比原理圖

- 關鍵字:

FPGA Verilog

- 傳統的硬件實現哈夫曼編碼的方法主要有:預先構造哈夫曼編碼表,編碼器通過查表的方法輸出哈夫曼編碼[1];編碼器動態生成哈夫曼樹,通過遍歷節點方式獲取哈夫曼編碼[2-3]。第一種方法從平均碼長角度看,在很多情況下非最優;第二種方法需要生成完整的哈夫曼樹,會產生大量的節點,且需遍歷哈夫曼樹獲取哈夫曼編碼,資源占用多,實現較為麻煩。本文基于軟件實現[4]時,使用哈夫曼樹,會提出一種適用于硬件并行實現的新數據結構——字符池,通過對字符池的頻數屬性比較和排序來決定各個字符節點在字符池中的歸屬。配置字符池的同時逐步生成

- 關鍵字:

verilog 哈夫曼編碼 字符池 FPGA 201712

- 寫verilog代碼要有硬件的概念-因為Verilog是一種硬件描述語言,所以在寫Verilog語言時,首先要有所要寫的module在硬件上如何實現的概念,而不是去想編譯器如何去解釋這個module

- 關鍵字:

verilog FPGA

- 一個合格FPGA 工程師的基本要求-一個合格的FPGA工程師需要掌握哪些知識?這里根據自己的一些心得總結一下,其他朋友可以補充啊。

- 關鍵字:

FPGA Verilog

- Verilog設計中的一些避免犯錯的小技巧-這是一個在設計中常犯的錯誤列表,這些錯誤常使得你的設計不可靠或速度較慢,為了提高你的設計性能和提高速度的可靠性你必須確定你的設計通過所有的這些檢查。

- 關鍵字:

FPGA Verilog

- 基于verilog的FPGA編程經驗總結-用了半個多月的ISE,幾乎全是自學起來的,碰到了很多很多讓人DT好久的小問題,百度也百不到,后來還是都解決了,為了盡量方便以后的剛學ISE的童鞋不再因為一些小問題而糾結,把這幾天的經驗總結了一下。好了,廢話不多說,上料!

- 關鍵字:

verilog FPGA

- verilog語言實現任意分頻-原文出自:分頻器是指使輸出信號頻率為輸入信號頻率整數分之一的電子電路。在許多電子設備中如電子鐘、頻率合成器等,需要各種不同頻率的信號協同工作,常用的方法是以穩定度高的晶體振蕩器為主振源,通過變換得到所需要的各種頻率成分,分頻器是一種主要變換手段。

- 關鍵字:

verilog 分頻器 電子電路

- 深入分析verilog阻塞和非阻塞賦值-學verilog 一個月了,在開發板上面寫了很多代碼,但是始終對一些問題理解的不夠透徹,這里我們來寫幾個例子仿真出阻塞和非阻塞的區別

- 關鍵字:

verilog 阻塞 非阻塞

- Verilog HDL簡明教程(2)-模塊是Verilog 的基本描述單位,用于描述某個設計的功能或結構及其與其他模塊通信的外部端口。

- 關鍵字:

Verilog HDL

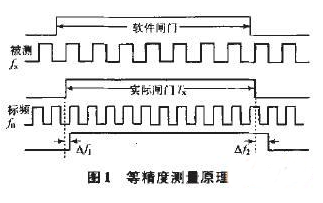

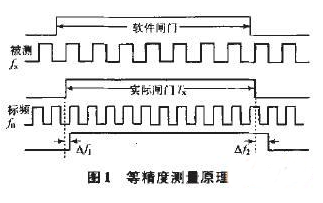

- 引言 傳統測量頻率的方法主要有直接測量法、分頻測量法、測周法等,這些方法往往只適用于測量一段頻率,當被測信號的頻率發生變化時,測量的精度就會下降。本文提出一種基于等精度原理的測量頻率的方法,在整個頻率測量過程中都能達到相同的測量精度,而與被測信號的頻率變化無關。本文利用FPGA(現場可編程門陣列)的高速數據處理能力,實現對被測信號的測量計數;利用單片機的運算和控制能力,實現對頻率、周期、脈沖寬度的計算及顯示。 等精度測量原理等精度測量的一個最大特點是測量的實際門控時間不是一個固定值,而

- 關鍵字:

Verilog FPGA

verilog-a介紹

您好,目前還沒有人創建詞條verilog-a!

歡迎您創建該詞條,闡述對verilog-a的理解,并與今后在此搜索verilog-a的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473