H.264/AVC中量化的Verilog實現

H.264作為新一代的視頻壓縮標準,是由ITU-T的視頻編碼專家組和ISO/IEC的MPEG(運動圖像編碼專家組)成立的聯合視頻小組共同開發的。它優異的壓縮性能也將在數字電視廣播、視頻實時通信、網絡視頻流媒體傳遞以及多媒體通信等各個方面發揮重要的作用。

在核心技術上,H.264/AVC采用各種有效的技術,如統一的VLC符號編碼、1/4像素精度的運動估計、多模式運動估計、基于4×4塊的整數變換、分層編碼語法等。由于采用了整數變換,計算不會出現浮點數,而且精度高等。這些措施使得H.264算法具有很高的編碼效率。在量化方面,量化步長采用52個,下面將主要分析量化。在此,提出量化的Verilog實現,將變換后的數據作為輸入,以量化后的碼流作為輸出,達到量化的目的。

1量化的功能介紹

取樣后的脈沖信號在時間上是離散的,但在幅值和空間上仍是連續的,即其可能取的值有無限多個,這就需要對它采用四舍五入的方法,將其可能的幅值數由無限多個變為有限個值。這種將信號幅值由連續量變成離散量的過程稱為量化。

在不降低視覺效果的前提下,量化過程可減少圖像編碼長度,減少視覺恢復中不必要的信息。H.264采用標量量化技術,將每個圖像樣點編碼映射成較小的數值。一般標量量化器的原理為:

式中:y為輸入樣本點編碼;QP為量化步長;FQ為y的量化值;round()取整函數(其輸出與輸入實數最近的整數)。

2量化的算法介紹

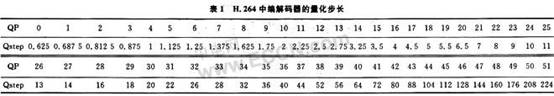

在H.264中,量化步長Qstep共有52個值。如表1所示。其中,QP是量化參數,是量化步長的序號。當QP取最小值0時,代表最精細的量化;當QP取最大值51時,代表最粗糙的量化。QP每增加6,Qstep增加1倍。應用時可以在這個較寬的量化步長范圍根據實際需要靈活選擇。對于色度編碼,一般使用與亮度編碼同樣的量化步長。為了避免在較高量化步長時出現顏色量化人工效應,現在的H.264草案把色度的QP最大值大約限制在亮度QP最大值的80%范圍內。最后的H.264草案規定,亮度QP的最大值是51;色度QP的最大值是39。

在H.264中,量化過程是對DCT的結果進行操作:

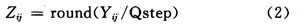

式中:Yij是矩陣Y中的轉換系數;Zij是輸出的量化系數;Qstep是量化步長。

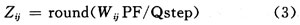

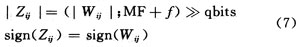

H.264量化過程還要同時完成DCT變換中“Ef”乘法運算,它可以表述為:

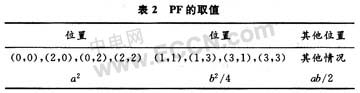

式中:Wij是矩陣W中的轉換系數;PF是矩陣EF中的元素。根據樣本點在圖像中的位置(i,j)取值如表2所示。

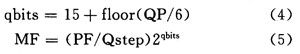

利用量化步長隨量化參數每增加6而增加1倍的性質,可以進一步簡化計算,即:

式中:floor()為取整函數(其輸出不大于輸入實數的最大整數)。式(3)可以寫為:

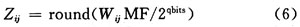

這樣,MF可以取整數。表3給出對應QP值為0~5的MF值。對于QP值大于5的情況,只是qbits值隨QP值每增加6而增加1,而對應的MF值不變。這樣,量化過程為整數運算,可以避免使用除法,確保用16位算法來處理數據,在沒有PSNR性能惡化的情況下,實現最小的運算復雜度如表3所示。

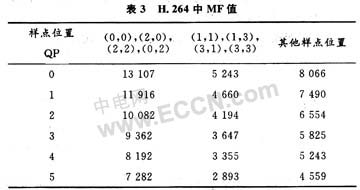

具體量化過程的運算為:

式中:“》”為右移運算,右移1次完成整數除以2;sign()為符號函數;f為偏移量。f的作用是改善恢復圖像的視覺效果,如對幀內預測圖像塊f取2qbits/3;對幀間預測圖像塊廠取2qbits/6。

3具體實現

在該文中,用Verilog語言實現H.264的量化;運用Modelsim進行仿真;用QuartusⅡ進行綜合。

根據Verilog編程,Modelsim仿真如圖1所示。

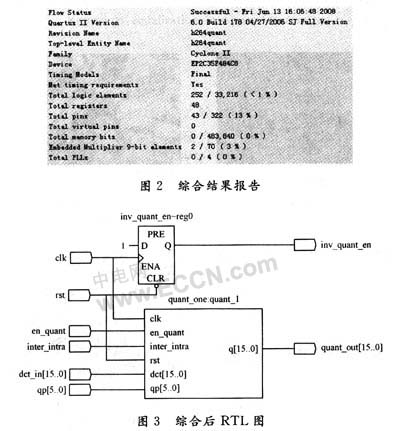

輸入的矩陣是[140,-1,-6,7,-19,-39,7,-92,22,17,8,31,-27,-32,-59,-21],最后量化的結果為[17,0,-1,0,-1,-2,0,-5,3,1,1,2,-2,-1,-5,-1]。由此可知,這與Iain E.G.Richardson給出的結果相符合。所用的開發板是紅色颶風第三代開發板,FPGA芯片是Altra EP2C35F484C8。從綜合后的報告可以看出,消耗的資源不到1%,如圖2所示。綜合后的RTL圖如圖3所示。

4結 語

介紹了H.264的量化算法,并用Modelsim進行了仿真,結果與理論完全一致。分析了在FPGA開發板上的資源的消耗。由此可知,完全可以用FPGA實現H.264的量化。

評論