實(shí)驗(yàn)10:七段數(shù)碼管

1. 實(shí)驗(yàn)?zāi)康?/strong>

本文引用地址:http://www.104case.com/article/202310/451311.htm(1)熟悉和掌握FPGA開發(fā)流程和Lattice Diamond軟件使用方法;

(2)通過實(shí)驗(yàn)理解和掌握數(shù)碼管驅(qū)動(dòng);

(3)學(xué)習(xí)用Verilog HDL描述數(shù)碼管驅(qū)動(dòng)電路。

2. 實(shí)驗(yàn)任務(wù)

在數(shù)碼管上顯示數(shù)字。

3. 實(shí)驗(yàn)原理

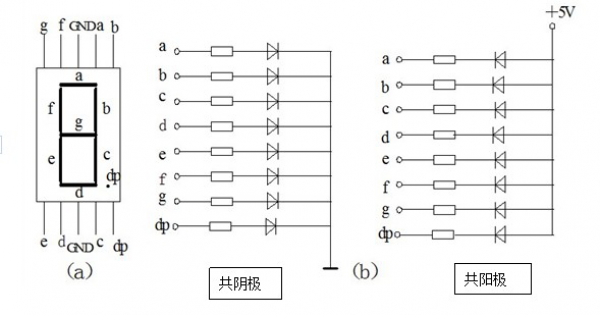

數(shù)碼管是工程設(shè)計(jì)中使用很廣的一種顯示輸出器件。一個(gè)7段數(shù)碼管(如果包括右下的小點(diǎn)可以認(rèn)為是8段)分別由a、b、c、d、e、f、g位段和表示小數(shù)點(diǎn)的dp位段組成。實(shí)際是由8個(gè)LED燈組成的,控制每個(gè)LED的點(diǎn)亮或熄滅實(shí)現(xiàn)數(shù)字顯示。通常數(shù)碼管分為共陽極數(shù)碼管和共陰極數(shù)碼管,結(jié)構(gòu)如下圖所示:

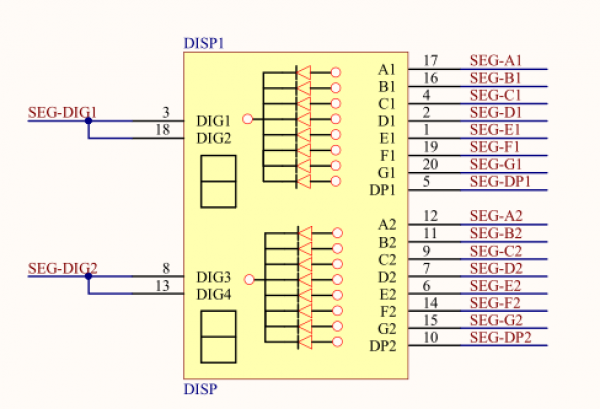

共陰8段數(shù)碼管的信號端低電平有效,而共陽端接高電平有效。當(dāng)共陽端接高電平時(shí)只要在各個(gè)位段上加上相應(yīng)的低電平信號就可以使相應(yīng)的位段發(fā)光。比如:要使a段發(fā)光,則在a段信號端加上低電平即可。共陰極的數(shù)碼管則相反。 可以看到數(shù)碼管的控制和LED的控制有相似之處,在小腳丫STEP-MXO2 V2開發(fā)板上有兩位共陰極數(shù)碼管:

數(shù)碼管所有的信號都連接到FPGA的管腳,作為輸出信號控制。FPGA只要輸出這些信號就能夠控制數(shù)碼管的那一段LED亮或者滅。這樣我們可以通過開關(guān)來控制FPGA的輸出,和3. 3-8譯碼器實(shí)驗(yàn)一樣,通過組合邏輯的輸出來控制數(shù)碼管顯示數(shù)字,下面是數(shù)碼管顯示的表格

這其實(shí)是一個(gè)4-16譯碼器,如果我們想數(shù)碼管能顯示16進(jìn)制可以全譯碼,如果只想顯示數(shù)字,可以只利用其中10個(gè)譯碼

4. 用CircuitJS查看

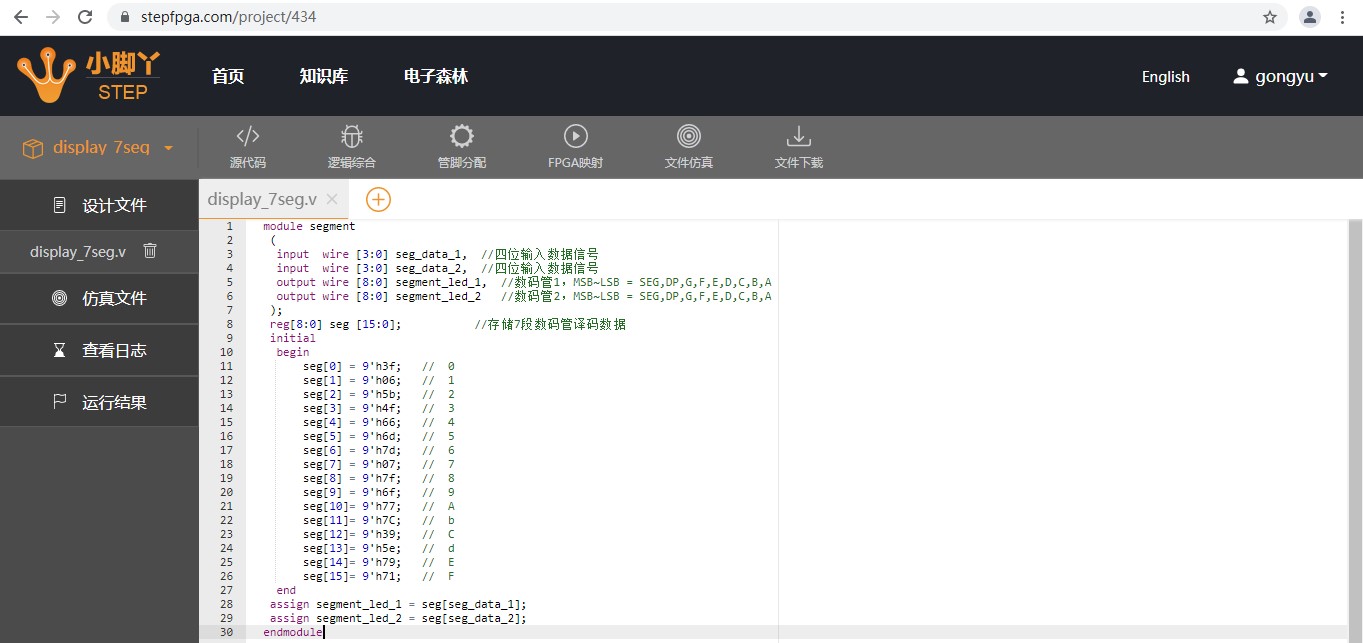

5. Verilog HDL建模描述

數(shù)碼管驅(qū)動(dòng)清單segment.v

module segment

(

input wire [3:0] seg_data_1, //四位輸入數(shù)據(jù)信號

input wire [3:0] seg_data_2, //四位輸入數(shù)據(jù)信號

output wire [8:0] segment_led_1, //數(shù)碼管1,MSB~LSB = SEG,DP,G,F,E,D,C,B,A

output wire [8:0] segment_led_2 //數(shù)碼管2,MSB~LSB = SEG,DP,G,F,E,D,C,B,A

);

reg[8:0] seg [15:0]; //存儲7段數(shù)碼管譯碼數(shù)據(jù)

initial

begin

seg[0] = 9'h3f; // 0

seg[1] = 9'h06; // 1

seg[2] = 9'h5b; // 2

seg[3] = 9'h4f; // 3

seg[4] = 9'h66; // 4

seg[5] = 9'h6d; // 5

seg[6] = 9'h7d; // 6

seg[7] = 9'h07; // 7

seg[8] = 9'h7f; // 8

seg[9] = 9'h6f; // 9

seg[10]= 9'h77; // A

seg[11]= 9'h7C; // b

seg[12]= 9'h39; // C

seg[13]= 9'h5e; // d

seg[14]= 9'h79; // E

seg[15]= 9'h71; // F

end

assign segment_led_1 = seg[seg_data_1];

assign segment_led_2 = seg[seg_data_2];

endmodule

6. 實(shí)驗(yàn)步驟

1 登錄小腳丫FPGA Web IDE系統(tǒng),建立工程

2 新建Verilog HDL設(shè)計(jì)文件,并鍵入設(shè)計(jì)代碼

3 設(shè)定該代碼位頂層文件

4 點(diǎn)擊“邏輯綜合”按鈕,完成綜合,代碼無錯(cuò)誤會(huì)顯示完成

5 點(diǎn)擊管腳分配,根據(jù)代碼中端口的定義綁定相應(yīng)的管腳

6 點(diǎn)擊“FPGA映射”生成可以配置FPGA的JED代碼

7 點(diǎn)擊文件下載,并鼠標(biāo)指向“下載JED文件”,鼠標(biāo)右鍵保存到STEPFPGA盤中完成FPGA的編程

7. 顯示效果

評論