基于Verilog語(yǔ)言的等精度頻率計(jì)設(shè)計(jì)

本文引用地址:http://www.104case.com/article/201708/362968.htm

引言

傳統(tǒng)測(cè)量頻率的方法主要有直接測(cè)量法、分頻測(cè)量法、測(cè)周法等,這些方法往往只適用于測(cè)量一段頻率,當(dāng)被測(cè)信號(hào)的頻率發(fā)生變化時(shí),測(cè)量的精度就會(huì)下降。本文提出一種基于等精度原理的測(cè)量頻率的方法,在整個(gè)頻率測(cè)量過(guò)程中都能達(dá)到相同的測(cè)量精度,而與被測(cè)信號(hào)的頻率變化無(wú)關(guān)。本文利用FPGA(現(xiàn)場(chǎng)可編程門(mén)陣列)的高速數(shù)據(jù)處理能力,實(shí)現(xiàn)對(duì)被測(cè)信號(hào)的測(cè)量計(jì)數(shù);利用單片機(jī)的運(yùn)算和控制能力,實(shí)現(xiàn)對(duì)頻率、周期、脈沖寬度的計(jì)算及顯示。

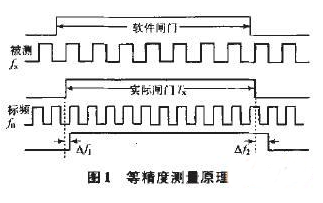

等精度測(cè)量原理等精度測(cè)量的一個(gè)最大特點(diǎn)是測(cè)量的實(shí)際門(mén)控時(shí)間不是一個(gè)固定值,而是一個(gè)與被測(cè)信號(hào)有關(guān)的值,剛好是被測(cè)信號(hào)的整數(shù)倍。在計(jì)數(shù)允許時(shí)間內(nèi),同時(shí)對(duì)標(biāo)準(zhǔn)信號(hào)和被測(cè)信號(hào)進(jìn)行計(jì)數(shù),再通過(guò)數(shù)學(xué)公式推導(dǎo)得到被測(cè)信號(hào)的頻率。由于門(mén)控信號(hào)是被測(cè)信號(hào)的整數(shù)倍,就消除了對(duì)被測(cè)信號(hào)產(chǎn)生的士1誤差,但是會(huì)產(chǎn)生對(duì)標(biāo)準(zhǔn)信號(hào)士1的誤差。如圖1所示。

系統(tǒng)中,如果采用的標(biāo)準(zhǔn)信號(hào)源的精度很高,就叮以達(dá)到一個(gè)很高的測(cè)量精度,一般情況下都是采用晶體作為標(biāo)準(zhǔn)信號(hào)源,因此可以達(dá)到很高的精度,滿足一般系統(tǒng)的要求。

2、FPGA模塊設(shè)計(jì)

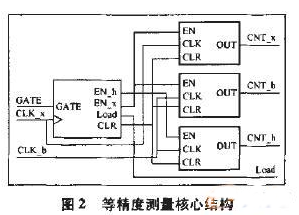

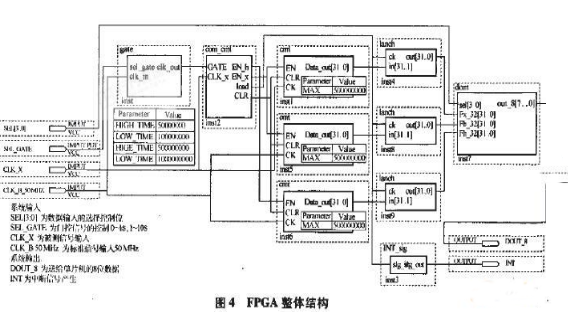

本系統(tǒng)在傳統(tǒng)的等精度測(cè)量原理基礎(chǔ)上進(jìn)行了改進(jìn)和優(yōu)化。增加了測(cè)量占空比的功能,同時(shí)由FPGA內(nèi)部產(chǎn)生清零信號(hào),節(jié)省了資源。改進(jìn)后的FPGA核心模塊如圖2所示。FPGA部分主要由門(mén)控信號(hào)產(chǎn)生模塊、計(jì)數(shù)器控制模塊、計(jì)數(shù)器模塊、鎖存器、中斷輸出、數(shù)據(jù)選擇輸出、頂層模塊組成。

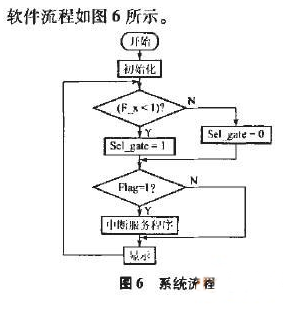

1)門(mén)控信號(hào)為了測(cè)量頻率為1H:的信號(hào),要求系統(tǒng)的開(kāi)門(mén)時(shí)間不小于1s;同理,為了測(cè)量0.1H:頻率的信號(hào),要求開(kāi)門(mén)時(shí)間最短為109。但是如果系統(tǒng)一直采用10s的門(mén)控信號(hào),測(cè)量高頻信號(hào)的等待時(shí)間太長(zhǎng),顯然不合理,因?yàn)闇y(cè)量結(jié)果的顯示必須要等到一個(gè)測(cè)量周期結(jié)束之后才能更新。本系統(tǒng)采用的方法是,由單片機(jī)給FPGA提供一個(gè)門(mén)控的選擇信號(hào),如果FPG人測(cè)得的頻率小于1Hz,那么單片機(jī)自動(dòng)給出一個(gè)啟動(dòng)10s門(mén)控的控制信號(hào);反之,如果發(fā)現(xiàn)測(cè)量的頻率大于1Hz,自動(dòng)切換回1。門(mén)控,實(shí)現(xiàn)了一個(gè)閉環(huán)的自動(dòng)控制,很好地解決了門(mén)控的時(shí)間問(wèn)題。

2)計(jì)數(shù)器控制模塊

該模塊是本文的創(chuàng)新點(diǎn)所在,主要用來(lái)同步被測(cè)信號(hào)。由前面的分析可知,門(mén)控信號(hào)啟動(dòng)(上升沿)后,在被測(cè)信號(hào)的上升沿啟動(dòng)計(jì)數(shù)允許模塊,允許計(jì)數(shù)器計(jì)數(shù);門(mén)控信號(hào)關(guān)閉(下降沿)后,在被測(cè)信號(hào)的下一個(gè)上升沿關(guān)閉計(jì)數(shù)允許模塊,停止計(jì)數(shù),從而保證了門(mén)控信號(hào)是被測(cè)信號(hào)的整數(shù)倍,達(dá)到了等精度的目的。該模塊有GATE,CLKx這2個(gè)輸人端;ENh,ENx,Load,CLR這4個(gè)輸出端。GATE為上一級(jí)給出的門(mén)控信號(hào)漢LKesx為被測(cè)信號(hào);EN-h,高電平期間對(duì)標(biāo)準(zhǔn)信號(hào)進(jìn)行計(jì)數(shù),得到CNT_h;EN_x為給出的允許計(jì)數(shù)信號(hào),在EN-x的高電平期間,對(duì)被測(cè)信號(hào)、標(biāo)準(zhǔn)信號(hào)同時(shí)計(jì)數(shù),得到CNT-x,CNT-b;Load為鎖存信號(hào);CLR為計(jì)數(shù)器清零信號(hào)。

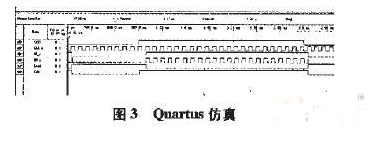

由CNTx和CNT_b可以計(jì)算出被測(cè)信號(hào)的頻率和周期;由CNTex和CNTh可以計(jì)算出被測(cè)信號(hào)的脈沖寬度。佑直圖加圖3所式。

3)計(jì)數(shù)器模塊

在設(shè)計(jì)計(jì)數(shù)器的過(guò)程中需要注意計(jì)數(shù)器的寬度設(shè)置,系統(tǒng)中采用的最大門(mén)控時(shí)間為10a,標(biāo)準(zhǔn)信號(hào)源的頻率為50MHz,則在計(jì)數(shù)的允許時(shí)間內(nèi)計(jì)數(shù)的最大值為:536870912,為了方便數(shù)據(jù)傳輸,系統(tǒng)中采用了32位位寬的計(jì)數(shù)器。

4)鎖存器模塊

在門(mén)控信號(hào)關(guān)閉的同時(shí),停止計(jì)數(shù),同時(shí)啟動(dòng)鎖存模塊,把測(cè)量的數(shù)據(jù)鎖存起來(lái),以便傳輸。

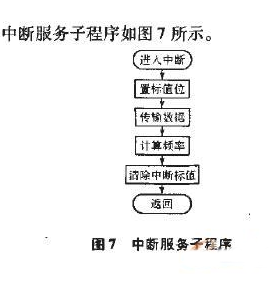

5)中斷輸出

鎖存數(shù)據(jù)的同時(shí),給單片機(jī)一個(gè)低電平的中斷信號(hào),通知單片機(jī)讀取數(shù)據(jù)。

6)數(shù)據(jù)選擇輸出模塊

系統(tǒng)中采用了3個(gè)32位的計(jì)數(shù)器,由于單片機(jī)采用的是51系列單片機(jī),只有8位的數(shù)據(jù)總線,所以一次通信只能傳輸8位數(shù)據(jù),3x32/8二12,所以設(shè)計(jì)了一個(gè)數(shù)據(jù)輸出控制模塊,由單片機(jī)提供4根地址線,譯碼后可以選擇16組數(shù)據(jù),單片機(jī)得到中斷通知后,分12次讀取測(cè)量的數(shù)據(jù)。

7)頂層模塊

實(shí)例化所有的底層模塊,同時(shí)為了調(diào)試方便,加入了一些測(cè)試點(diǎn)。FPGA部分的整體結(jié)構(gòu)圖如圖4所示。

3、單片機(jī)模塊控制

3.1理論分析

在計(jì)數(shù)允許EN-x時(shí)間內(nèi),對(duì)被測(cè)信號(hào)和標(biāo)準(zhǔn)信號(hào)同時(shí)進(jìn)行進(jìn)行計(jì)數(shù),得到CNT_x和CNT_b,設(shè)被測(cè)信號(hào)的周期為T(mén),,頻率為Fx,標(biāo)準(zhǔn)信號(hào)周期為F6.頻率為Fb。則有:

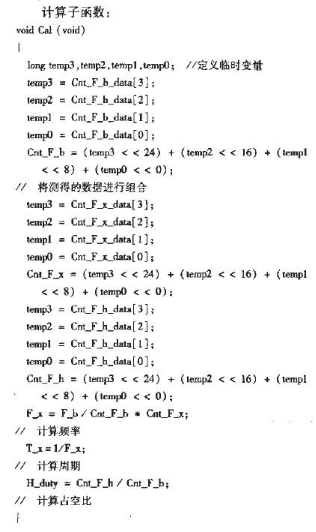

系統(tǒng)中采用式(6)一式(8)進(jìn)行計(jì)算,得到最終的測(cè)量數(shù)據(jù),單片機(jī)中采用浮點(diǎn)數(shù)進(jìn)行運(yùn)算,計(jì)算的精度可以滿足系統(tǒng)的要求。

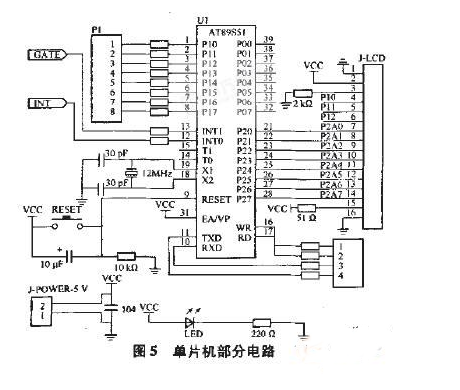

3.2硬件電路

系統(tǒng)硬件電路比較簡(jiǎn)單,就是單片機(jī)的最小系統(tǒng)加上液晶顯示模塊,設(shè)計(jì)時(shí)需要注意,51單片機(jī)端口電壓是5V輸出,而FPGA是3.3V輸出,所以在數(shù)據(jù)傳輸時(shí)要串聯(lián)一個(gè)電阻一般1000一300f2即可。電路原理圖如圖5所示。

3.3軟件設(shè)計(jì)

單片機(jī)軟件主要由系統(tǒng)初始化、數(shù)據(jù)傳輸、頻率、周期、占空比計(jì)算、液晶顯示等程序模塊組成。

下面簡(jiǎn)單介紹主函數(shù)及計(jì)算子函數(shù)。軟件流程如圖6所示。

中斷服務(wù)子程序如圖7所示。

4、結(jié)束語(yǔ)

本系統(tǒng)設(shè)計(jì)采用FPGA和單片機(jī)結(jié)合的方式實(shí)現(xiàn)等精度測(cè)量頻率,充分發(fā)揮了FPGA高速的數(shù)據(jù)處理能力以及單片機(jī)的計(jì)算、控制能力。采用Verilog硬件描述語(yǔ)言對(duì)系統(tǒng)進(jìn)行仿真測(cè)試.最終下載到FPGA內(nèi)部。單片機(jī)采用C語(yǔ)言編寫(xiě)程序,利用浮點(diǎn)數(shù)進(jìn)行計(jì)算,精度高。同時(shí)設(shè)計(jì)了門(mén)控信號(hào)自動(dòng)選擇的閉環(huán)控制,大大地提高了系統(tǒng)的性能。等精度測(cè)量技術(shù)在生產(chǎn)、實(shí)驗(yàn)等環(huán)境中得到了廣泛的應(yīng)用。

評(píng)論