fpga-nios 文章 最新資訊

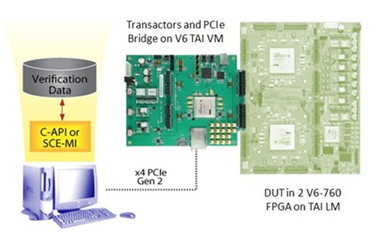

S2C為Xilinx原型驗(yàn)證系統(tǒng)提供突破性驗(yàn)證模塊技術(shù)

- S2C 日前宣布其Verification Module技術(shù)(專利申請(qǐng)中)已可用于其基于Xilinx的FPGA原型驗(yàn)證系統(tǒng)中。V6 TAI Verification Module可以實(shí)現(xiàn)在FPGA原型驗(yàn)證環(huán)境和用戶驗(yàn)證環(huán)境之間高速海量數(shù)據(jù)傳輸。用戶可以使用Xilinx ChipScope或者第三方調(diào)試環(huán)境,同時(shí)查看4個(gè)FPGA。另外,V6 TAI Verification Module還可以用于1.3M~4.7M ASIC門的原型設(shè)計(jì)。V6 TAI Verification Module具有PCIe G

- 關(guān)鍵字: S2C Xilinx FPGA

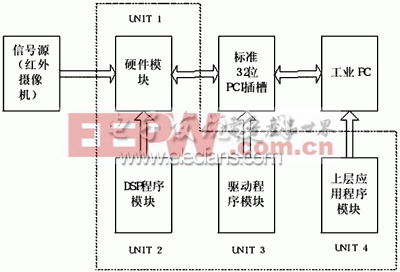

一款用DSP+FPGA實(shí)現(xiàn)的數(shù)字相關(guān)器

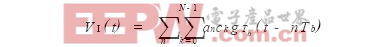

- 引 言數(shù)字相關(guān)器作為軟件無線電的典型應(yīng)用,在擴(kuò)頻通信中成為必不可少的技術(shù)。在傳統(tǒng)的擴(kuò)頻通信中,采用模擬器件(如:聲表面波器) 來實(shí)現(xiàn)解擴(kuò)單元,而用數(shù)字相關(guān)器可以增加系統(tǒng)的靈活性和穩(wěn)定性,因此,對(duì)數(shù)字相關(guān)器

- 關(guān)鍵字: 相關(guān) 數(shù)字 實(shí)現(xiàn) FPGA DSP

Altera演示第一款基于模型的FPGA浮點(diǎn)DSP工具

- Altera公司日前演示了使用FPGA的浮點(diǎn)DSP新設(shè)計(jì)流程,這是業(yè)界第一款基于模型的浮點(diǎn)設(shè)計(jì)工具,支持在FPGA中實(shí)現(xiàn)復(fù)數(shù)浮點(diǎn)DSP算法。伯克萊設(shè)計(jì)技術(shù)公司 (Berkeley Design Technology, Inc, BDTI) 進(jìn)行的獨(dú)立分析驗(yàn)證了能夠在Altera 的Stratix 和Arria FPGA系列中簡單方便的高效實(shí)現(xiàn)高性能浮點(diǎn)DSP設(shè)計(jì)。

- 關(guān)鍵字: Altera FPGA

fpga-nios介紹

您好,目前還沒有人創(chuàng)建詞條fpga-nios!

歡迎您創(chuàng)建該詞條,闡述對(duì)fpga-nios的理解,并與今后在此搜索fpga-nios的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對(duì)fpga-nios的理解,并與今后在此搜索fpga-nios的朋友們分享。 創(chuàng)建詞條

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會(huì)員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司