- 美國國家儀器有限公司(National Instruments,簡稱NI)作為致力于為工程師和科學家提供解決方案來應對全球最嚴峻的工程挑戰的供應商,今日宣布推出LabVIEW通信系統設計套件,該套件結合了軟件無線電(SDR)硬件和完整的軟件設計流程,旨在助力工程師開發5G系統原型。

過去,無線通信原型是由獨立的設計團隊使用各自的設計工具來進行開發。LabVIEW通信系統設計套件開發環境可幫助整個設計團隊通過統一的抽象表示來獲得從算法到FPGA的整體認識。該方法使得設計工程師能夠專注于創新而無需將

- 關鍵字:

LabVIEW 無線電 FPGA

- 賽靈思公司亞太區銷售與市場副總裁楊飛先生在CSIA-ICCAD 2014 (中國集成電路設計業2014年會暨中國內地與香港集成電路產業協作發展高峰論壇) 上發表題為“保持領先一代優勢,為中國半導體行業提速加油”的主題演講,通過介紹賽靈思業界最大容量FPGA 及其在仿真模擬和原型設計領域的領導地位,展示了賽靈思為中國半導體行業發展提速的能力,并表達了其致力于服務和支持中國創新的承諾。

根據“集成電路產業“十二五”發展規劃”,集

- 關鍵字:

賽靈思 FPGA

- 賽靈思公司亞太區銷售與市場副總裁楊飛先生在CSIA-ICCAD 2014 (中國集成電路設計業2014年會暨中國內地與香港集成電路產業協作發展高峰論壇)展示手中的賽靈思ASIC級UltraScale 系列產品, 其中包括業界最大容量的半導體器件 ——20nm Virtex UltraScale VU440 3D IC。 楊飛同時也發布了一個激動人心的消息:VU440樣片已經出貨并計劃于2015年 1月(也就是下個月)交付客戶,敬請期待。

楊飛表示, 3D 芯片在世界范圍內

- 關鍵字:

Xilinx FPGA ASIC

- 隨著ARM處理器架構的興起和32位微控制器的廣泛應用,人們很容易假設,隨著32位處理器芯片的價格和功耗的下降,采用8位MCU進行設計已經變得越來越沒有競爭力了。

但現實情況并非如此。Atmel、Microchip和意法半導體等芯片供應商比以往任何時候更致力于完善和升級自己的8位微控制器,并正為其添加高性能外設和擴展開發工具。

所謂“兩手都要抓,兩手都要硬”,Atmel似乎深諳其中的道理,為了鞏固微控制器市場的地位,近日,Atmel在北京召開發布會,推出了全新的8位A

- 關鍵字:

Atmel MCU

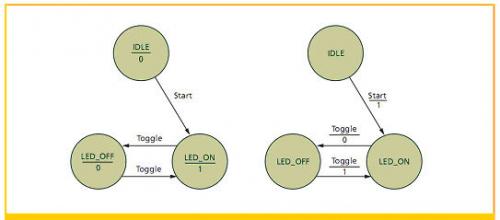

- FPGA常常用于執行基于序列和控制的行動,比如實現一個簡單的通信協議。對于設計人員來說,滿足這些行動和序列要求的最佳方法則是使用狀態機。狀 態機是在數量有限的狀態之間進行轉換的邏輯結構。一個狀態機在某個特定的時間點只處于一種狀態。但在一系列觸發器的觸發下,將在不同狀態間進行轉換。

理論上講,狀態機可以分為Moore狀態機和Mealy狀態機兩大類。它們之間的差異僅在于如何生成狀態機的輸出。Moore狀態機的輸出僅為當前 狀態的函數。典型的例子就是計數器。而Mealy狀態機的輸出是當前狀態和輸入的函

- 關鍵字:

FPGA 狀態機

- 物聯天下、傳感先行。而傳感器與MCU的融合,被認為是物聯網時代的新潮流。

- 關鍵字:

物聯網 傳感器 MCU

- 個人認為, 嵌入式編程最難的兩部分就是interrupt和MM(memory manage),有些人可能感覺不到,那是因為太多數情況下芯片制造商都幫你寫好了,但是如果你本身就在為芯片制造商工作,那你就必須自己會寫配置文件了,這兩個東西之所以比較難是因為要用匯編或類C來寫,屬于比較低層的東西,中斷有外部中斷和內部中斷,外部中斷有兩種實現模式,硬件中斷模式和軟件中斷模式,相對來說比較簡單,屬于應用層面的,相比之下,內部中斷就要復雜得多,內部中斷主要是發生重起,總線出錯,溢出,校驗出錯等情況產生的,很多軟件

- 關鍵字:

嵌入式編程 ADC MCU

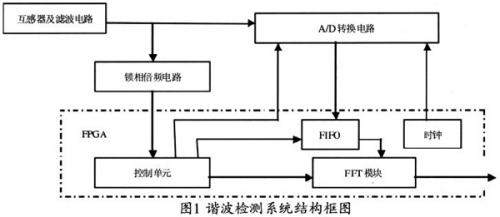

- 基于FFT算法的電力系統諧波檢測裝置,大多采用DSP芯片設計。DSP芯片是采用哈佛結構設計的一種CPU,運算能力很強,速度很快;但是其順序 執行的模式限制了其進行FFT運算的速度。而現場可編程邏輯門陣列(Field Programmable Gate Array, FPGA)在近年來獲得了突飛猛進的發展,目前已成為實現數字系統的主流平臺之一。與DSP相比,FPGA最大的優勢就是可以進行并行計算。在進行FFT 這類并行運算為主的算法時,采用FPGA的優勢不言而喻。用FPGA實現FFT算法進行諧波檢測成為

- 關鍵字:

Xilinx FPGA DSP

- 現場可編程器件(FPGA和CPLD)等ISP器件無須編程器,利用器件廠商提供的編程套件,采用自頂而下的模塊化設計方法,使用原理圖或硬件描述語言(VHDL)等方法來描述電路邏輯關系,可直接對安裝在目標板上的器件編程。它易學、易用、簡化了系統設計,減小了系統規模,縮短設計周期,降低了生產設計成本,從而給電子產品的設計和生產帶來了革命性的變化。

1、系統結構及工作原理

LED點陣顯示控制的傳統方式是采用單片機或系統機作為CPU來實現,當系統顯示的信息比較多時,由于單片機的輸入/輸出端口(I/O)

- 關鍵字:

CPLD LED FPGA

- 隨著社會的發展和信息時代對各類信息快速發布的需要, 許多政府部門和企事業單位從提高自身形象和信息規范化管理考慮, 廣泛采用LED 電子顯示屏顯示產品, 此類多媒體顯示系統通過一定的控制方式,用于顯示文字、圖形、圖像、動畫、股市行情等各種信息以及電視、錄像、DVD 等信號, 是交通指揮引導、部隊作戰、電力部門、公共場所進行企業形象宣傳、信息發布和精神文明建設的有效工具和良好窗口。

采用現場可編程邏輯器件( FPGA) 作為控制器, 選擇合適的器件, 利用器件豐富的I/O 口、內部邏輯和連線資源,

- 關鍵字:

FPGA LED ALTERA

- 一 設計概述

1.1目標領域和主要應用

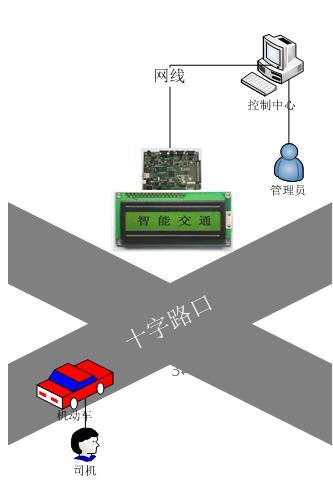

如今,交通在現代人的生活中所占比重越來越重要。如何安全,高效的利用道路資源是每個人都要面對的問題。現有車載GPS導航只能查看到道路走向信息,卻不能查看到道路上的各種突發情況,比如交通事故、堵車現象、交通臨時管制、禁止部分車輛通行、臨時禁止左右轉、道路維修、道路更改的情況。這時如果有能夠實時更新并對外發布和顯示交通信息、道路狀況信息和設施狀況等,能起到減少堵塞程度,提高道路通行能力的作用。也間接提高了交通運輸,人們出行的效率。

該項目是基于FPG

- 關鍵字:

FPGA LCD GPS

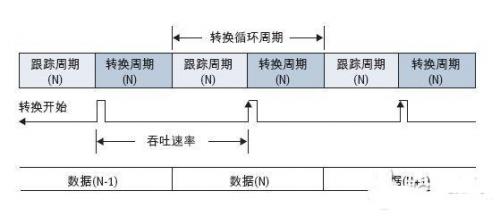

- 使用MCU的系統設計人員受益于摩爾定律,即通過更小封裝、更低成本獲得更多的豐富特性功能。嵌入式系統設計人員和MCU廠商關心數據采集系統的三個基本功能:捕獲、計算和通信。理解全部功能對設計大有幫助,本文將主要關注數據采集系統的捕獲階段。

捕獲

復雜的混合信號MCU必須能夠從模擬世界中捕獲某些有用信息,并且能夠把連續時間信號轉換成離散的數字形式。模數轉換器(ADC)是完成這項任務最重要的MCU外設,因此ADC的性能往往決定何種MCU適用于何種應用。MCU也能夠通過各種串行或并行數字I/O接口捕

- 關鍵字:

MCU ADC

- 項目背景及可行性分析

2.1 項目名稱及摘要:

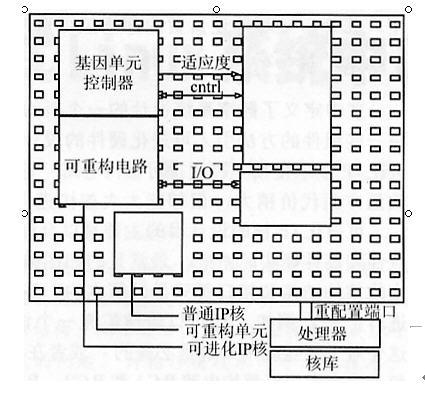

基于fpga二維小波變換核的實時可重構電路

現場可編程門陣列為可進化設計提供了一個理想的模板。FPGAs 提供了一個硬件環境 ,這個環境 可將邏輯物理實現和 布線資源 按照為了特定功能所配置的比特流而重新組織構建起來。 RTR設計工具 繞過傳統的fpga綜合以及比特流生成過程 使可進化設計成為可能. JBits工具套裝 就為在Xilinx 的Virtex系列和4000系列設備上進行RTR設計提供了一個設計環境。

這個項目旨在利用J

- 關鍵字:

fpga 小波變換 IP核

- 管腳是FPGA重要的資源之一,FPGA的管腳分別包括,電源管腳,普通I/O,配置管腳,時鐘專用輸入管腳GCLK等。

(1)電源管腳:

通常來說: FPGA內部的電壓包括內核電壓和I/O電壓。

1.內核電壓:即FPGA內部邏輯的供電。通常會較I/O電壓較低,隨著FPGA的工藝的進度,FPGA的內核電壓逐漸下降,這也是降低功耗的大勢所趨。

2.I/O電壓 (Bank的參考電壓)。每個BANK都會有獨立的I/O電壓輸入。也就是每個BANK的參考電壓設定后,本BANK上所有I/O的電平

- 關鍵字:

FPGA GCLK

- 首先依次回答上篇提出的幾個問題:

第一個問題:如何避免狀態機產生lacth 示例如下,通過在always(*)語句塊中,添加默認賦值,ns_state = cs_state;

always@(*)

ns_state = cs_state;

case(cs_state)

idle :

if(start)

ns_state = op1_state;

op0_state :

if(op0_over)

ns_state = op1_state;

- 關鍵字:

FPGA 狀態機

fpga+mpu+mcu介紹

您好,目前還沒有人創建詞條fpga+mpu+mcu!

歡迎您創建該詞條,闡述對fpga+mpu+mcu的理解,并與今后在此搜索fpga+mpu+mcu的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473