信號在PCB走線中傳輸時延

信號在媒質中傳播時,其傳播速度受信號載體以及周圍媒質屬性決定。在PCB(印刷電路板)中信號的傳輸速度就與板材DK(介電常數),信號模式,信號線與信號線間耦合以及繞線方式等有關。隨著PCB走線信號速率越來越高,對時序要求較高的源同步信號的時序裕量越來越少,因此在PCB設計階段準確知道PCB走線對信號時延的影響變的尤為重要。本文基于仿真分析DK,串擾,過孔,蛇形繞線等因素對信號時延的影響。

本文引用地址:http://www.104case.com/article/275997.htm1.引言

信號要能正常工作都必須滿足一定的時序要求,隨著信號速率升高,數字信號的發展經歷了從共同步時鐘到源同步時鐘以及串行(serdes)信號。在當今的消費類電子,通信服務器等行業,源同步和串行信號占據了很大的比重。串行信號比如常見PCIE,SAS,SATA,QPI,SFP+,XUAI,10GBASE-KR等信號,源同步信號比如DDR信號。

串行信號在發送端將數據信號和時鐘(CLK)信號通過編碼方式一起發送,在接收端通過時鐘數據恢復(CDR)得到數據信號和時鐘信號。由于時鐘數據在同一個通道傳播,串行信號對和對之間在PCB上傳輸延時要求較低,主要依靠鎖相環(PLL)和芯片的時鐘數據恢復功能。

源同步時鐘主要是DDR信號,在DDR設計中,DQ(數據)信號參考DQS(數據選通)信號,CMD(命令)信號和CTL(控制)信號參考CLK(時鐘)信號,由于DQ的速率是CMD DDR2/ DDR3.DDR4預計在2015年將成為消費類電子的主要設計,隨著DDR信號速率的不斷提高,在DDR4設計中特別是DQ和DQS之間傳輸時延對設計者提出更高的挑戰。

在PCB設計的時候為了時序的要求需要對源同步信號做一些等長,一些設計工程師忽略了這個信號等長其實是一個時延等長,或者說是一個‘時間等長’。

2.傳輸時延簡介

Time delay又叫時延(TD),通常是指電磁信號或者光信號通過整個傳輸介質所用的時間。在傳輸線上的時延就是指信號通過整個傳輸線所用的時間。

Propagation delay又叫傳播延遲(PD),通常是指電磁信號或者光信號在單位長度的傳輸介質中傳輸的時間延遲,與“傳播速度”成反比例(倒數)關系,單位為“Ps/inch”或“s/m”。

從定義中可以看出時延=傳播延遲*傳輸長度(L)

其中v為傳播速度,單位為inch/ps或m/s c為真空中的光速(3X108 m/s)

εr為介電常數PD為傳播延遲,單位為Ps/inch或s/m TD為信號通過長度為L的傳輸線所產生的時延L為傳輸線長度,單位為inch或m

從上面公式可以知道,傳播延遲主要取決于介質材料的介電常數,而傳播時延取決于介質材料的介電常數、傳輸線長度和傳輸線橫截面的幾何結構(幾何結構決定電場分布,電場分布決定有效介電常數)。嚴格來說,不管是延遲還是時延都取決于導體周圍的有效介電常數。在微帶線中,有效介電常數受橫截面的幾何結構影響比較大;而串擾,其有效介電常數受奇偶模式的影響較大;不同繞線方式有效介電常數受其繞線方式的影響。

3.仿真分析過程

3.1微帶線和帶狀線傳輸時延

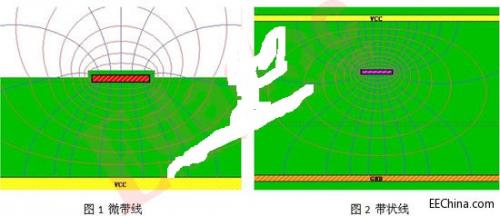

PCB中微帶線是指走線只有一個參考面,如下圖1;帶狀線是指走線有2個參考面,如下圖2。

帶狀線由于電磁場都被束縛在兩個參考面之間的板材中,所以走線的有效介電常數為板材的介電常數。

微帶線會導致部分電磁場暴露在空氣中,空氣的相對介電常數約為1.0006,板材如常規FR4的介電常數為4.2,那么微帶線的有效介電常數在1和4.2之間,可以利用下面的公式計算微帶線的有效介電常數「Collins,1992」:

εe = (εr +1)/2 + (εr -1)/2(1+12H/W)-1/2 + F -0.217(εr -1)T/√WH 3.1 F = 0.02 (εr -1)(1-W/H)2 (W/H 1) 3.2

其中,εe為有效介電常數,εr為電路板材料的介電常數,H為導線高于地平面的高度,W為導線寬度,T為導線厚度。

圖4微帶線層疊與時延

圖5帶狀線層疊和時延

在圖4和圖5的層疊結構下,1000mil的走線時延差=179.729ps-147.954ps=31.775ps,可以看出這個差距是非常大的。在做源同步的DDR同組等長時候只考慮物理等長會帶來很嚴重的'時間不等長。

3.2走線和過孔傳輸時延

在PCB設計時候,經常會遇到走線換層,走線換層必須借助于過孔。但長度相等的過孔和走線之間的時延并不相等。過孔的時延可以用式3.3表示

TD_via=√LC 3.3

其中TD_via表示信號經過過孔的時延,L表示過孔的寄生電感,C表示過孔的寄生電容。從式3.3可以看出寄生電容和寄生電感都會導致過孔的傳輸時延變大。而不同過孔結構寄生參數也會發生改變。下面通過仿真分析過孔時延和傳輸線時延時間的偏差。

圖6過孔結構及寄生參數

如圖6所示過孔結構時延可以根據式3.3計算出:

TD_via=√LC=sqr(0.4021pf*1326.2pH)=23.1ps式3.4

由式3.4可以看出,結構如圖6所示過孔的傳輸時延為23.1ps.而對于普通FR4板材的微帶線,1.6mm走線傳輸時延約為11ps,對于帶狀線約為12.5ps.通過計算可以看出相同長度的走線和過孔之間的時延相差是非常大的。因此對設計工程師來講設計的時候盡量做到以下兩點:

1)需要做等長的信號要盡量走同層,換層時需要注意總的長度要保持相等并且每層走線都需要等長。

2)需要等長的信號走相同走線層可以保持過孔的時延一致,從而消除過孔時延不一致帶來的影響。

模擬信號相關文章:什么是模擬信號

鎖相環相關文章:鎖相環原理

評論