- 工業物聯網(IIoT)互聯解決方案提供商RTI公司近日在DistribuTECH 2020國際大展的展覽和演示了兩個基于數據分發服務(DDS)標準的互操作性解決方案,有效地支持輸變電網克服現代化進程中所遇到的挑戰。Distributech 2020于1月28日至30日在德克薩斯州圣安東尼奧市舉行,是全球領先的年度輸電及配電行業大型會展活動。做為一項全球性年度盛事,DistribuTECH匯集了行業思想領袖以及全球公用事業、產品和服務提供商,共同應對電力行業遇到的最嚴峻挑戰。RTI公司在所展示的解決方案旨在

- 關鍵字:

lloT DDS

- 工業物聯網(IIoT)互連性解決方案提供商RTI公司近日宣布,聘任新一代微創心臟泵開發商Puzzle Medical Devices公司首席執行官Stuart Kozlick為RTI咨詢委員會的最新成員,為RTI公司醫療行業市場運營提供咨詢顧問。Stuart Kozlick將以其豐富的行業專業經驗,幫助RTI公司捕捉戰略發展機遇,擴大在IIoT行業的影響力。作為一名經驗豐富的高管,Stuart Kozlick在醫療設備開發、創新和研究方面擁有超過17年的經驗,能夠非常好地勝任其在RTI公司咨詢委員會的職務

- 關鍵字:

IIoT DDS

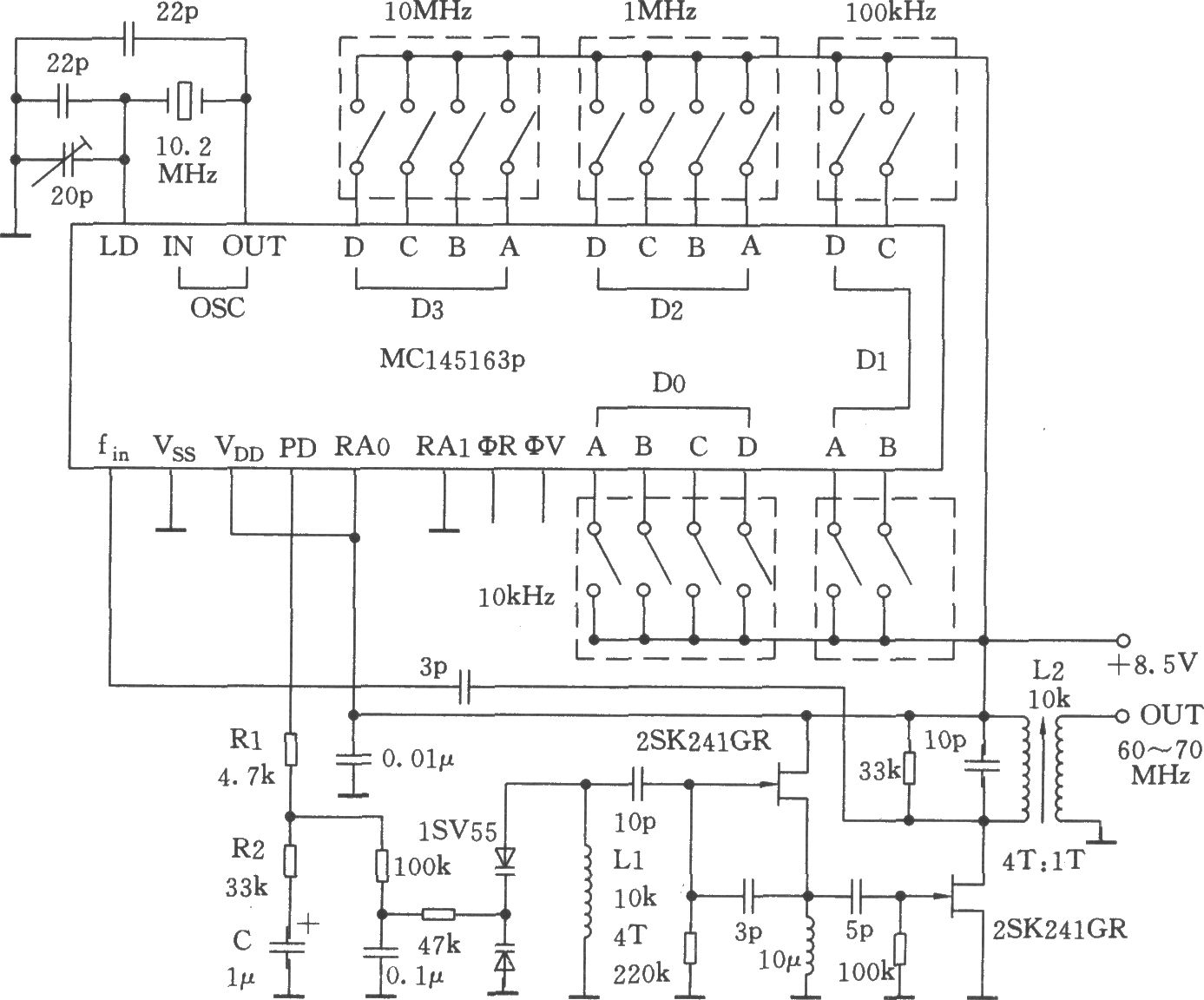

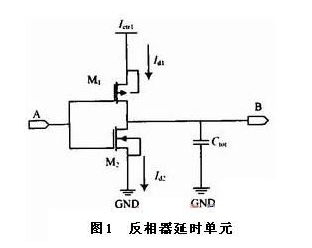

- 頻率合成技術起源于二十世紀30年代,當時所采用的頻率合成方法是直接頻率合成。它是利用混頻、倍頻、分頻的方法由參考源頻率經過加、減、乘、除

- 關鍵字:

DDS 雜散分析 方法

- 摘要 光伏匯流箱是光伏發電的重要組成部分,主要用于太陽能光伏組件與直流控制柜間的連接。文中設計的光伏匯流箱主電路以單片機STC12C5A60S2為控制核心,由電流檢測電路、溫度檢測電路、通信電路和電源電路等組成,主

- 關鍵字:

DDS AD9852 傳感器 電源

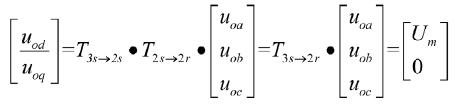

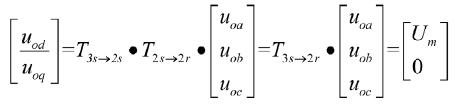

- 系統采用三相半橋拓撲,以STM32F407ZET6單片機為主從控制器,主控制器在dq坐標下進行控制實現三相穩壓輸出,從控制器采用主從均流控制實現兩臺三相逆變器的電流分配,采用三相同步鎖相環(SRP-PLL)。逆變器單獨工作時,輸出交流母線電壓為24.01 V,頻率為49.99 Hz,總諧波畸變率為1.63%,系統整體效率為92.33%,負載調整率為0.12%。逆變器并聯工作時,系統實現了兩臺逆變器輸出功率比可調,輸出線電流折算值誤差最大值為0.06 A,并聯工作負載調整率為0.21%。此外,系統具有友好的

- 關鍵字:

三相逆變器 主從均流 SPF-PLL 201809

- PLL(Phase Locked Loop): 為鎖相回路或鎖相環,用來統一整合時脈訊號,使內存能正確的存取資料。PLL用于振蕩器中的反饋技術。鎖相環通常由鑒相器(PD)、

- 關鍵字:

PLL 振蕩器 DCDC

- 功率分析儀在測試時出現的數據跳動、效率異常等現象,很多時候與信號的頻率是否準確測量有著很大的關系,本文就對頻率測量的重要性進行分析,希望能幫助大家進行更準確的測量。 首先我們來看看為什么頻率的測量對其他參數會造成如此大的影響。 同步源的選擇 用過功率分析儀的工程師一定會記得,在對儀器進行設置的時候,一個叫“同步源”的設置選項,該選項包括了各個測試通道的電壓和電流,工程師可以自主來進行選擇。該選項的選擇對直流信號測試影響不大,但對交流信號的測試會有很大的影響。原因是因為如果交流信號測量數據的間隔如

- 關鍵字:

PLL 頻率

- 1 頻綜布局 單頻綜布局。通常采取如圖形狀進行布局:左臂支為參考頻率源及鎖相環控制電路,右臂支為壓控制振蕩器(VCO)輸出隔離放大電路。中部環狀為鎖相環(PLL) 乒乓切換式頻綜布局,又叫音叉式布局:音叉的兩臂為對稱兩個 PLL 頻綜,臂交匯點為開關切換裝置。公共臂為切換后輸出放大兩路。 多通道收發接收機或者發射機本振電平分配電路布局:對稱樹狀布局。 2 混頻器(MIXER)電路布局 混頻電路又稱上下變頻電路,是發射機和超外差式接收機的重要組成部分,是一種典型的頻譜搬移電路。對于接收機來講,

- 關鍵字:

射頻,PLL

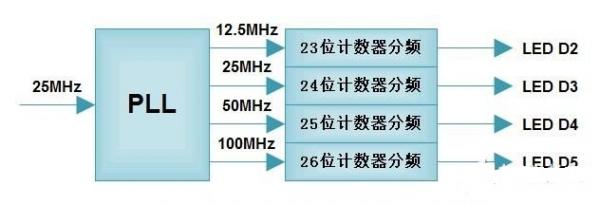

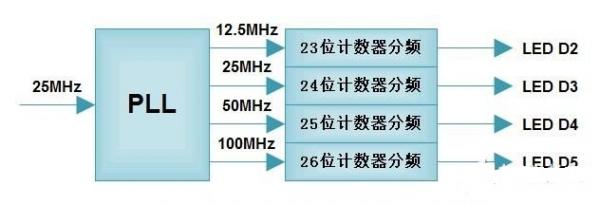

- 如圖8.17所示,本實例將用到FPGA內部的PLL資源,輸入FPGA引腳上的25MHz時鐘,配置PLL使其輸出4路分別為12.5MHz、25MHz、50MHz和100MHz的時鐘信號,這4路時鐘信號又分別驅動4個不同位寬的計數器不停的計數工作,這些計數器的最高位最終輸出用于控制4個不同的LED亮滅。由于這4個時鐘頻率都有一定的倍數關系,所以我們也很容易通過調整合理的計數器位寬,達到4個LED閃爍一致的控制。

cy4.v模塊代碼解析 先來看cy4.v模塊的

- 關鍵字:

FPGA PLL

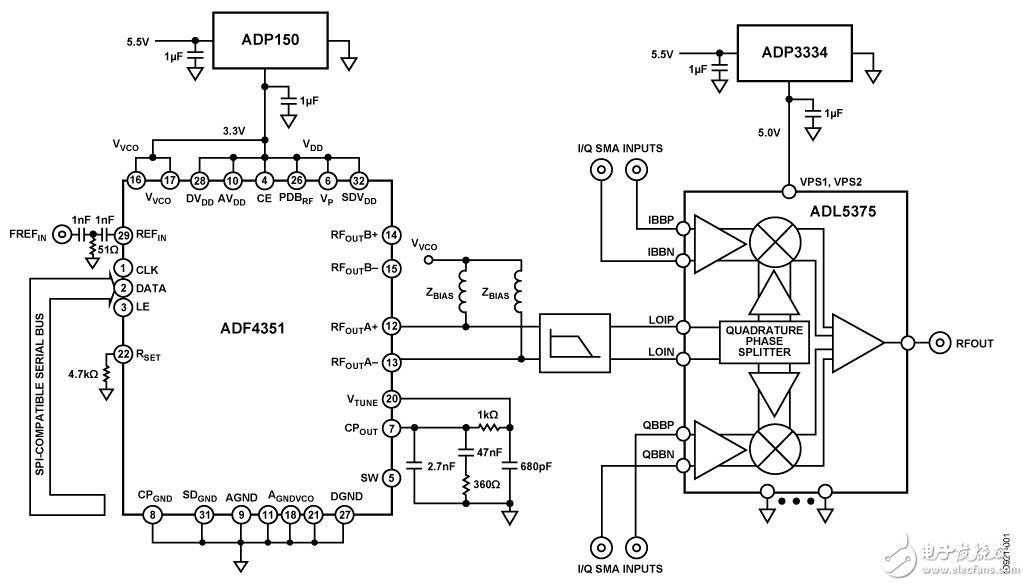

- 寬帶低誤差矢量幅度(EVM)直接變頻發射機原理圖-本電路為寬帶直接變頻發射機模擬部分的完整實現方案(模擬基帶輸入、RF輸出)。通過使用鎖相環(PLL)和寬帶集成電壓控制振蕩器(VCO),本電路支持500 MHz至4.4 GHz范圍內的RF頻率。對來自PLL本振(LO)進行諧波濾波,確保提供出色的正交精度、邊帶抑制和低EVM。

- 關鍵字:

VCO PLL ADI 變頻發射機

- 利用可編程振蕩器增強FPGA應用-可編程時鐘振蕩器用作FPGA系統的時序參考,可提供一系列優勢。其中首要優勢是為了實現時鐘樹優化而進行高分辨率頻率選擇時所帶來的設計靈活性,另一個巨大優勢是具有可以減少電磁干擾(EMI)的擴頻調制功能。

- 關鍵字:

DLL PLL FPGA

- 基于單片機與FPGA的直接頻率數字合成器的設計方案-本文提出了一種基于單片機的直接頻率數字合成器的設計方案。方案采用單片機控制FPGA產生DDS信號輸出頻率范圍為20Hz~20KHz,幅度為0.3V~5V,兩路正交信號能夠實現0o~359o的相位差,并通過MAX+plusII軟件進行仿真驗證。仿真結果表明,本方案可達到預定要求,具有較強的實用性。

- 關鍵字:

頻率合成器 DDS

- PLL和DLL:都是鎖相環,區別在哪里?-一般在altera公司的產品上出現PLL的多,而xilinux公司的產品則更多的是DLL,開始本人也以為是兩個公司的不同說法而已,后來在論壇上見到有人在問兩者的不同,細看下,原來真是兩個不一樣的家伙。

- 關鍵字:

鎖相環 DLL PLL

- 制作一個基于STC15W4K48S4設計手機控制AD9850信號發生器的設計方案-任何發射機或接收機都需要一個源。這個源可以是RC振蕩器、LC振蕩器、晶體振蕩器、鎖相環頻率合成器或DDS直接數字頻率合成器。而DDS直接數字頻率合成器是近10幾年的新興方案。縱觀各種DDS芯片,數美國ADI公司的AD9850性價比最高。市面上滿天飛的一款DDS信號發生器就是采用此款芯片。出于成本和占有量的考慮,決定率先開發配套此款DDS信號發生器的控制板。本控制板硬件使用最新版STC的51系列單片機STC15W4K48S4。

- 關鍵字:

dds ad9850 振蕩器

- PLL鎖相環的特性、應用與其基本工作過程-PLL(Phase Locked Loop),也稱為鎖相環路(PLL)或鎖相環,它能使受控振蕩器的頻率和相位均與輸入參考信號保持同步,稱為相位鎖定,簡稱鎖相。

- 關鍵字:

pll 鎖相環

dds+pll介紹

您好,目前還沒有人創建詞條dds+pll!

歡迎您創建該詞條,闡述對dds+pll的理解,并與今后在此搜索dds+pll的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473