利用可編程振蕩器增強FPGA應用

當今復雜的FPGA含有眾多用于實現各種電路與系統的功能塊,諸如邏輯陣列、存儲器、DSP 模塊、處理器、用于時序生成的鎖相環 (PLL) 和延遲鎖定環 (DLL)、標準I/O、高速數字收發器以及并行接口(PCI、DDR 等)。這些不同的功能塊通常由多個時鐘驅動,FPGA 一般會綜合采用外部振蕩器以及內部PLL 與DLL來生成時鐘。系統設計人員必須決定如何綜合使用外部與內部資源來實現最佳的時鐘樹設計。而可編程時鐘振蕩器用作FPGA 系統的時序參考,可提供一系列優勢。其中首要優勢是為了實現時鐘樹優化而進行高分辨率頻率選擇時所帶來的設計靈活性。另一個巨大優勢是具有可以減少電磁干擾 (EMI) 的擴頻調制功能。

本文引用地址:http://www.104case.com/article/201710/367164.htm內在可編程的硅MEMS時鐘振蕩器架構能夠幫助采用FPGA的系統設計人員解決許多難題。這種微型機電系統架構能夠輕松整合一些其它功能,如:用于消減EMI 的擴頻時鐘、用于消除抖動的數控振蕩器以及高速應用中的失效保護功能。

頻率選擇

一般系統需要一系列時鐘頻率。其中一些是標準頻率,這種標準化可能是出于對行業規范強制要求的考慮(如:PCI Express要求的100MHz 頻率),也可能是由于得到了廣泛的應用(如:用于SATA 的75MHz 或用于PCITM 的33.333 MHz)。上述頻率與 I/O接口關聯在一起,以確保實現互操作性,因為接口兩側可能不屬于同一系統。與此相對,用戶可選擇用于驅動處理器、DSP和狀態機引擎的時鐘頻率,以優化速度、功率或資源占用。

在進行速度優化時, 應以最高時鐘頻率來驅動處理引擎,以使每秒運算次數達到最高。但是,時鐘周期抖動必須足夠低,以確保最小時鐘周期大于設計的臨界時序路徑,否則有可能出現邏輯錯誤。頻率選擇的常用方法是采用內部FPGA PLL對來自標準外部參考振蕩器的高頻時鐘進行綜合。此方法只有在內部 PLL 具有高頻分辨率和低抖動時才有效。

某些FPGA集成了內部低噪聲分數PLL,可滿足所有這些要求。在這種情況下,可以采用簡單的外部振蕩器參考。不過,許多情況下FPGA會采用帶有環形VCO和整數反饋分頻器的PLL來綜合不同頻率。這種PLL小巧靈活,比較容易設計和控制,而且功耗極低。不過,使用此類內部PLL時很難同時實現高分辨率與低抖動。

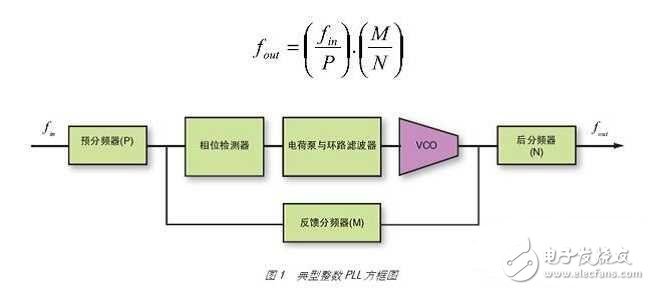

圖 1 為整數 PLL 的一般架構。對PLL 輸出頻率的編程需綜合采用預分頻器 (P)、反饋分頻器 (M) 和后分頻器 (N)來完成,如下式所示:

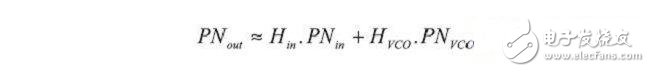

PLL反饋環路形成一個限帶控制系統。輸出周期抖動主要取決于參考時鐘相位噪聲 (PNIn ) 和內部 VCO 相位噪聲(PNVCO),如下式所示:

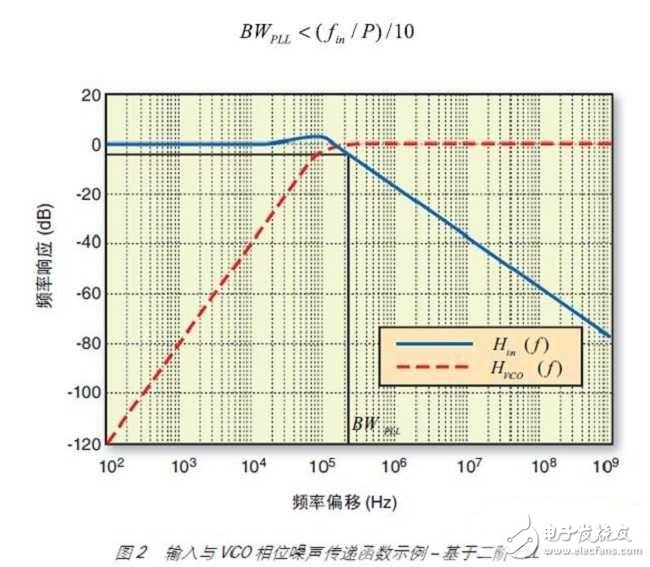

輸入參考時鐘相位噪聲和VCO相位噪聲與輸出相位噪聲息息相關,分別通過低通濾波器和高通濾波器響應來體現,如表達式中的Hin和HVCO。HVCO與Hin的截止頻率直接相關。圖 2 說明了典型二階PLL中Hin與HVCO的相互關系。最高PLL帶寬取決于相位檢測器的更新速率。大部分實際PLL 的最高實際帶寬極限如下式所示:

例如,如果PLL輸入頻率是40MHz并且P=40,則最高實際PLL帶寬是100kHz。

評論