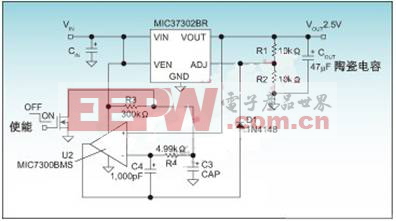

- IPTV系統中的FPGA供電問題解決方案介紹,目前越來越多的家用電器從低速的撥號上網向寬帶互聯網接入或互聯網協議電視(IPTV)轉移,尤其是IPTV有望在中國獲得快速的發展。比較而言,IPTV的基礎設施成本相當低,因為這種方法不需要銅軸電纜,而是采用DSL或寬帶鏈

- 關鍵字:

解決方案 介紹 問題 供電 系統 FPGA IPTV

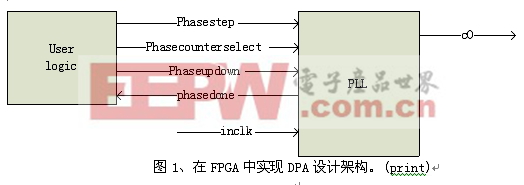

- 如何在低成本FPGA中實現動態相位調整,在FPGA中,動態相位調整(DPA)主要是實現LVDS接口接收時對時鐘和數據通道的相位補償,以達到正確接收的目的。ALTERA的高端FPGA,如STRATIX(r) 系列中自帶有DPA電路,但低端的FPGA,如CYCLONE(r)系列中是沒有的。本文主

- 關鍵字:

相位 調整 動態 實現 成本 FPGA 如何

- IIR數字濾波器設計-在FPGA上實現任意階IIR數字濾波器摘要:本文介紹了一種采用級聯結構在FPGA上實現任意階I...

- 關鍵字:

IIR數字濾波器 fpga

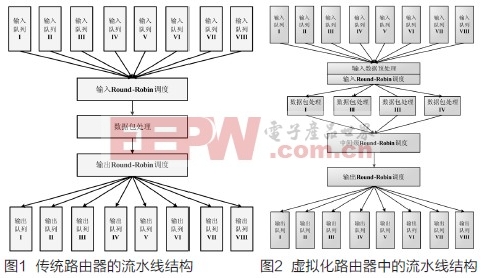

- 本文主要介紹了虛擬化路由器的結構以及其中的關鍵調度機制的算法和實現,通過多級的調度處理,實現了支持多個可靈活配置,線速轉發的路由實例的虛擬化路由器。本文所提到虛擬化路由器實際設計名稱為“IsoRouter”,它基于NetFPGA板卡,本文所介紹的調度機制不針對具體某一型號的FPGA,它可以在任何一款FPGA上實現。

- 關鍵字:

路由器 FPGA

- FPGA設計一個很重要的設計是時序設計,而時序設計的實質就是滿足每一個觸發器的建立(Setup)/保持(Hold)時間的要求。建立時間(Setup Time):是指在觸發器的時鐘信號上升沿到來以前,數據穩定不變的時間,如果建立時間

- 關鍵字:

FPGA 基礎 時序設計

- 1 引言賽車剎車系統是賽車系統上具有相對獨立功能的子系統,其作用是承受賽車的靜態重量、動態沖擊載荷以及吸收賽車剎車時的動能,實現賽車的制動與控制。其性能的好壞直接影響到賽車的快速反應、安全制動和生存能力,進

- 關鍵字:

CPLD DSP 防滑 剎車控制器

- 邏輯分析儀測試在基于FPGA的LCD顯示控制中的應用摘要:邏輯分析儀作為基礎儀器,應該在基礎數字電路教學中得到廣泛應用。本文介紹了基于FPGA的液晶顯示控制設計方案,通過使用OLA2032B邏輯分析儀,對控制線進行監測與

- 關鍵字:

FPGA LCD 邏輯分析儀 測試

- 摘要:首先介紹了兩種高精度相位差測量算法,一種是基于直接數字頻率合成(DDS)的相關測量法,另一種是基于快速傅里葉變換(FFT)的FFT測量法。其次,通過理論仿真分析兩種算法在不同信噪比和數據長度下的性能,并在此基

- 關鍵字:

FPGA 高精度 測量算法 相位差

- 直接數字頻率合成(DDS)技術是美國學者J.Tierncy,C.M.Rader和B.Gold在1971年首次提出的。這是一種全數字技術,該技術從相位概念出發直接合成所需要的波形。同傳統的頻率合成技術相比,DDS技術具有很多優點:頻率切

- 關鍵字:

頻率 合成 DDS 數字 直接 單片機 CPLD 實現 利用

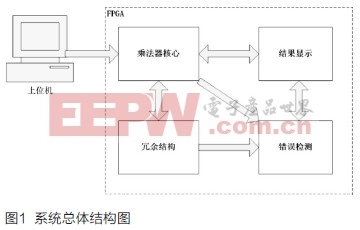

- 現場可編程門陣列(Field Programmable Gate Array,FPGA)可通過用戶軟件編程來配置生成硬件電路,極大提高了電子系統設計中的靈活性和通用性,因而被廣泛應用于航天、通信、醫療和工控等重要領域。但在空間環境中,基于SRAM的FPGA容易受SEU(Single Event Upset)和SETs(Single Event Transients)的影響,從而導致系統故障。DMR(Dual Modular Redundancy)和TMR(Triple Modular Redundancy

- 關鍵字:

乘法器 FPGA

- 0 引 言USB(通用串行總線)是英特爾、微軟、IBM、康柏等公司1994年聯合制定的一種通用串行總線規范,它解決了與網絡通信問題,而且端口擴展性能好、容易使用。最新的USB2.0支持3種速率:低速1.5 Mbit/s,全速12 Mbit/

- 關鍵字:

Verilog C68013 68013 FPGA

- 摘要:以單片機和可編程邏輯器件(FPGA)為控制核心,設計了一個程控濾波器,實現了小信號程控放大、程控調整濾波器截止頻率和幅頻特性測試的功能。其中放大模塊由可變增益放大器AD603實現,最大增益60dB,10dB步進可調

- 關鍵字:

FPGA 程控濾波器

- 摘要:為了擴展VME總線和CAN總線的應用范圍,充分利用兩種總線的不同傳輸特點,采用了模塊設計方法,提出一種基于FPGA和MCU的總線轉換方案。該方案給出了FPGA與上位VME總線部分的VME總線接口設計,利用MCU控制CPLD擴

- 關鍵字:

CAN-VME FPGA MCU 總線

cpld/fpga介紹

您好,目前還沒有人創建詞條cpld/fpga!

歡迎您創建該詞條,闡述對cpld/fpga的理解,并與今后在此搜索cpld/fpga的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473