- 本文介紹了電荷俘獲的原理以及直流特征分析技術對俘獲電荷進行定量分析的局限性。接下來,本文介紹了一種超快的脈沖I-V分析技術,能夠對具有快速瞬態充電效應(FTCE)的高k柵晶體管的本征(無俘獲)性能進行特征分析。

先進CMOS器件高k柵技術的進展

近年來,高介電常數(高k)材料,例如鉿氧化物(HfO2)、鋯氧化物(ZrO2)、氧化鋁(Al2O3)以及

- 關鍵字:

脈沖 CMOS

- SuVolta日前宣布推出PowerShrink?低功耗平臺。該平臺可以有效降低CMOS集成電路2倍以上的功耗,同時保持性能并提高良率。SuVolta和富士通半導體有限公司(Fujitsu Semiconductor Limited)今天還共同宣布,富士通已獲得授權使用SuVolta創新型PowerShrink?低功耗技術。

- 關鍵字:

SuVolta CMOS

- ?????? 6月9日,應用于高能效電子產品的首要高性能硅方案供應商安森美(ON Semiconductor)半導體推出五款超小封裝的低壓降(LDO) 線性穩壓器,強化用于智能手機及其他便攜電子應用的現有產品陣容。這些新器件基于互補金屬氧化物半導體(CMOS)技術,均能提供150毫安(mA)的輸出電流。

NCP4682和NCP4685超低電流穩壓器的供電電流僅為典型值1微安(μA),輸出電壓范圍為1.2伏(V)至3.3 V。

- 關鍵字:

安森美 CMOS NCP4682

- 基準電壓源可廣泛應用于A/D、D/A轉換器、隨機動態存儲器、閃存以及系統集成芯片中。使用0.18 μm CMOS工藝設計了具有高穩定度、低溫漂、低輸出電壓為0.6 V的CMOS基準電壓源。

- 關鍵字:

設計 電壓 基準 CMOS 0.18

- 摘要:設計了一種寬帶軌對軌運算放大器,此運算放大器在3.3 V單電源下供電,采用電流鏡和尾電流開關控制來實現輸入級總跨導的恒定。為了能夠處理寬的電平范圍和得到足夠的放大倍數,采用用折疊式共源共柵結構作為前

- 關鍵字:

CMOS 運算放大器

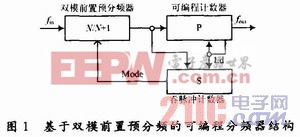

- 提出一種應用于射頻頻率合成器的寬分頻比可編程分頻器設計。該分頻器采用脈沖吞吐結構,可編程計數器和吞脈沖計數器都采用改進的CMOS源極耦合(SCL)邏輯結構的模擬電路實現,相對于采用數字電路實現降低了電路的噪聲和減少了版圖面積。同時,對可編程分頻器中的檢測和置數邏輯做了改進,提高分頻器的工作頻率及穩定性。最后,采用TSMC的0.13/μm CMOS工藝,利用Cadence Spectre工具進行仿真,在4.5 GHz頻率下,該分頻器可實現200~515的分頻比,整個功耗不超過19 mW,版圖面積為106 μ

- 關鍵字:

可編程 設計 CMOS 合成器 頻率 應用

- 以網絡攝像機為應用背景,闡述了數字CMOS圖像傳感器OV7720芯片的參數、接口和通信協議,結合網絡攝像機的開發環境,詳細介紹了芯片與嵌入式CPU的硬件電路和軟件結構。系統以嵌入式Linux作為操作系統,相機芯片OV7720,OV529對數字視頻進行采集、壓縮編碼并生成MPEG-4碼流。MPEG-4碼流經過AT91SAM7X256控制器外掛的網絡芯片被輸送到PC機。PC機端通過內嵌MPEG-4解壓插件的IE瀏覽器實時瀏覽視頻和控制網絡攝像機的狀態。

- 關鍵字:

網絡 攝像機 設計 OV7720 傳感器 CMOS 圖像 基于

- 摘要:為解決PWM控制器中輸出電壓與基準電壓的誤差放大問題,設計了一款高增益、寬帶寬、靜態電流小的新型誤差放大器,通過在二級放大器中間增加一級緩沖電路,克服補償電容的前饋效應,同時消除補償電容引入的零點。

- 關鍵字:

CMOS PWM 誤差放大器

- 摘要:提出了一種新穎的CMOS四象限模擬乘法器電路,該乘法器基于交叉耦合平方電路結構,并采用減法電路來實現。它采用0.18mu;m CMOS工藝,使用HSPICE軟件仿真。仿真結果顯示,該乘法器電路在1.8 V的電源電壓下工作

- 關鍵字:

法器 設計 模擬 CMOS 線性 低壓

- 摘要:為適應低壓低功耗設計的應用,設計了一種超低電源電壓的軌至軌CMOS運算放大器。采用N溝道差分對和共模電平偏移的P溝道差分對來實現軌至軌信號輸入。當輸入信號的共模電平處于中間時,P溝道差分對的輸入共模電平

- 關鍵字:

CMOS 軌至軌 運算放大器

- 摘要:為了提高運算放大器的驅動能力,依據現有CMOS集成電路生產線,介紹一款新型BiCMOS集成運算放大電路設計,探討BiCMOS工藝的特點。在S-Edit中進行“BiCMOS運放設計”電路設計,并對其電路各個器件參數

- 關鍵字:

BiCMOS CMOS 工藝 放大器設計

- 結合電荷泵型LED驅動器的工作要求,從減小輸出電壓紋波、穩定輸出電壓出發,設計了一款誤差放大器。該誤差放大器具有較大的工作電壓范圍,使電荷泵型LED驅動器高效率低噪聲工作。基于CHRT 0.35μm CMOS MIXEDSIGNAL TECHNOLOGY進行仿真,結果表明,在2.7~5 V工作電壓范圍內,開環電壓增益約等于72 dB,相位裕度約等于65°,單位增益帶寬約等于4.6 MHz,共模抑制比CMRR約等于113 dB,電源抑制比PSRR約等于100 dB。

- 關鍵字:

放大器 設計 誤差 CMOS LED 驅動器 電荷

cmos-ldo介紹

您好,目前還沒有人創建詞條cmos-ldo!

歡迎您創建該詞條,闡述對cmos-ldo的理解,并與今后在此搜索cmos-ldo的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473