EEPW首頁(yè) >>

主題列表 >>

asic ip核

asic ip核 文章 最新資訊

邁向先進(jìn)制程 PLD商機(jī)更加龐大

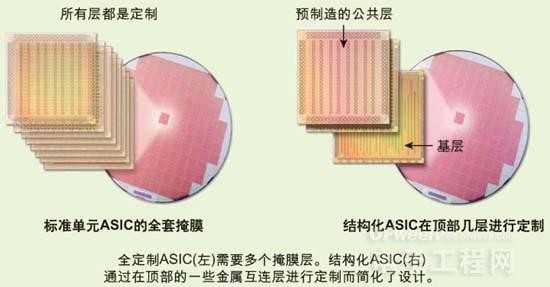

- 在過(guò)去的幾年間,整個(gè)半導(dǎo)體產(chǎn)業(yè)面臨著巨幅的衰退,然而,這個(gè)衰退現(xiàn)象卻為可編程邏輯組件(PLD)產(chǎn)業(yè)帶來(lái)了實(shí)質(zhì)的絕佳成長(zhǎng)機(jī)會(huì)。雖然PLD公司之間的競(jìng)爭(zhēng)仍然相當(dāng)激烈,但ASIC仍然是主要的競(jìng)爭(zhēng)對(duì)手,如今,這種競(jìng)爭(zhēng)現(xiàn)象已經(jīng)快速轉(zhuǎn)變?yōu)槭袌?chǎng)強(qiáng)烈喜好可編程解決方案的傾向。 目前,以先進(jìn)制程來(lái)實(shí)行ASIC設(shè)計(jì)的成本,已經(jīng)約是十年前的三倍,面對(duì)這些開(kāi)發(fā)成本的劇幅提升,許多ASIC設(shè)計(jì)師迫使必須仰賴(lài)具有合理的經(jīng)濟(jì)性、但在制程技術(shù)落后的方案。采用較舊的技術(shù)會(huì)有效能上的劣勢(shì),例如將會(huì)限制住ASIC設(shè)計(jì)師在先進(jìn)設(shè)計(jì)中支

- 關(guān)鍵字: PLD ASIC

Xilinx的CEO談半導(dǎo)體業(yè)的進(jìn)步論

- Xilinx的CEO Moshe Gavrielov在接受電子周刊的獨(dú)家系列釆訪時(shí),談到從過(guò)去的12個(gè)月到未來(lái)semi工業(yè)面臨的挑戰(zhàn)與機(jī)會(huì)。 從2009年開(kāi)始過(guò)去半導(dǎo)體工業(yè)的那種類(lèi)推模式的發(fā)展已不能適用于目前的半導(dǎo)體公司及未來(lái)的全球電子市場(chǎng)的生存需要。 此次經(jīng)濟(jì)的下降周期加速了技術(shù)與貿(mào)易挑戰(zhàn),同時(shí)由于產(chǎn)品可移動(dòng)性和無(wú)限連結(jié)的市場(chǎng)需求,使得產(chǎn)品設(shè)計(jì)的復(fù)雜性和風(fēng)險(xiǎn)度提高。所以要求設(shè)計(jì)公司必須提高產(chǎn)品進(jìn)入市場(chǎng)的精準(zhǔn)度,嚴(yán)格控制成本開(kāi)支,尤其是在ASIC和ASSP電路設(shè)計(jì)中必須重視的工程費(fèi)用的不斷

- 關(guān)鍵字: Xilinx 半導(dǎo)體 ASIC

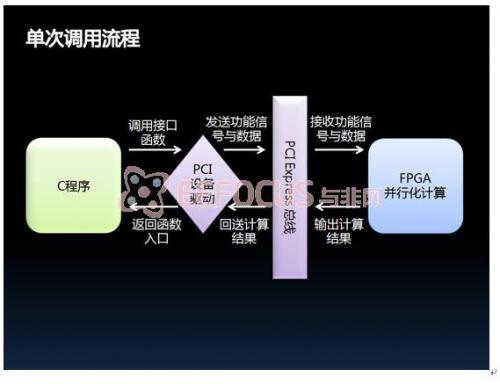

華虹NEC推出高效nvSOC產(chǎn)品原型平臺(tái)

- 世界領(lǐng)先的純晶圓代工廠之一,上海華虹NEC電子有限公司(以下簡(jiǎn)稱(chēng)“華虹NEC”)日前宣布成功推出nvSOC產(chǎn)品原型平臺(tái),這一平臺(tái)的推出可以幫助客戶(hù)高效創(chuàng)建SOC和ASIC原型,大大縮短客戶(hù)SOC產(chǎn)品開(kāi)發(fā)周期和減少設(shè)計(jì)風(fēng)險(xiǎn)。 nvSOC平臺(tái)的硬件主要由通用FPGA芯片和華虹NEC特有的平臺(tái)核心IP芯片構(gòu)成,其中平臺(tái)核心IP芯片是指集成了華虹NEC 某一種NVM(Non Volatile Memory, 包括Flash,EEPROM,OTP等)工藝平臺(tái)的NVM模塊和基礎(chǔ)模擬/

- 關(guān)鍵字: 華虹NEC 晶圓代工 SOC ASIC

基于FPGA的8段數(shù)碼管動(dòng)態(tài)顯示IP核設(shè)計(jì)

- 設(shè)計(jì)基于FPGA的8段數(shù)碼管動(dòng)態(tài)顯示IP核,介紹8段數(shù)碼管內(nèi)部結(jié)構(gòu)及其驅(qū)動(dòng)顯示方式和IP核設(shè)計(jì)方法,給出8段數(shù)碼管動(dòng)態(tài)顯示IP核的Verilog HDL程序源代碼及其C語(yǔ)言驅(qū)動(dòng)程序。此IP核可例化成1~8個(gè)共陰極(或共陽(yáng)極)數(shù)碼管控制器,能方便地控制1~8個(gè)數(shù)碼管同時(shí)顯示數(shù)字和小數(shù)點(diǎn)位。測(cè)試結(jié)果表明,該IP核工作可靠、穩(wěn)定,可直接應(yīng)用于電子設(shè)計(jì)中。

- 關(guān)鍵字: FPGA 8段數(shù)碼管 動(dòng)態(tài)顯示 IP核

MCU + USB設(shè)備控制器IP核的設(shè)計(jì)

- 關(guān)鍵字: MCU USB IP核 設(shè)備控制器

基于ASIC設(shè)計(jì)的手工綜合研究

- 針對(duì)IC前端設(shè)計(jì)中的關(guān)鍵技術(shù),即將寄存器傳輸級(jí)(RTL)描述的手工綜合成門(mén)級(jí)網(wǎng)表,通過(guò)人工參與的方式,運(yùn)用數(shù)字電路設(shè)計(jì)知識(shí)將行為級(jí)代碼用一些最基本的邏輯門(mén)(比如與非門(mén)、非門(mén)、或非門(mén)等)按照時(shí)應(yīng)的綜合電路模型得出其相應(yīng)的門(mén)級(jí)電路。在ASIC設(shè)計(jì)過(guò)程中運(yùn)用這種方法,不僅優(yōu)化電路的結(jié)構(gòu),且能保證邏輯功能的正確性,同時(shí)可降低傳輸過(guò)程中的延遲,提高芯片設(shè)計(jì)的可靠性。因此,研究ASCI設(shè)計(jì)中的手工綜合具有重要的實(shí)用價(jià)值。

- 關(guān)鍵字: ASIC

Open-Silicon、MIPS和Virage Logic共同完成ASIC處理器設(shè)計(jì)

- Open-Silicon、業(yè)界標(biāo)準(zhǔn)處理器架構(gòu)與內(nèi)核領(lǐng)導(dǎo)廠商 MIPS 科技公司和Virage Logic 三家公司共同宣布,已成功開(kāi)發(fā)一款測(cè)試芯片,充分展現(xiàn)出構(gòu)建高性能處理器系統(tǒng)的業(yè)界領(lǐng)先技術(shù)。該處理器測(cè)試芯片實(shí)現(xiàn)了1.1GHz的頻率速度,成功通過(guò)了65nm 芯片測(cè)試,使其成為65nm ASIC 中最快的處理器之一。同時(shí),后續(xù)40nm器件的開(kāi)發(fā)工作也已經(jīng)開(kāi)始進(jìn)行,目標(biāo)是超過(guò)2.5GHz頻率,并提供超過(guò)5000 DMIPS的性能。這項(xiàng)開(kāi)發(fā)計(jì)劃采用了Open-Silicon的CoreMAXTM技術(shù),以及超

- 關(guān)鍵字: MIPS ASIC 測(cè)試芯片 65nm 40nm

視頻監(jiān)控智能化趨勢(shì)走強(qiáng),應(yīng)用方案誰(shuí)主浮沉?

- 近些年,隨著全球安全意識(shí)提升,視頻監(jiān)控市場(chǎng)不斷增長(zhǎng)。盡管全球經(jīng)濟(jì)危機(jī)導(dǎo)致許多行業(yè)發(fā)展受阻,但ABIResear...

- 關(guān)鍵字: FPGA 視頻監(jiān)控 DSP ASIC

賽普拉斯和Cytech Global 簽訂分銷(xiāo)特許協(xié)議

- 賽普拉斯半導(dǎo)體公司日前宣布Cytech Global 公司將在印度和東南亞國(guó)家銷(xiāo)售賽普拉斯全部專(zhuān)屬和可編程解決方案。Cytech的母公司Macnica與賽普拉斯在日本具有長(zhǎng)期成功的合作伙伴關(guān)系。近來(lái),Macnica 香港公司(Macnica 的子公司)開(kāi)始在中國(guó)銷(xiāo)售賽普拉斯產(chǎn)品。雙方的合作協(xié)議即刻生效。 Cytech在亞太區(qū)的“需求創(chuàng)造引擎”擁有16個(gè)辦事處,超過(guò)200名雇員。其銷(xiāo)售隊(duì)伍技術(shù)背景深厚,能在整個(gè)設(shè)計(jì)過(guò)程中給與客戶(hù)大力協(xié)助。此外,該公司在銷(xiāo)售可編程和專(zhuān)屬解決方

- 關(guān)鍵字: 賽普拉斯 PSoC ASIC

ADI推出新型微處理器監(jiān)控IC

- ADI最新推出用于監(jiān)控手持式工業(yè)設(shè)備、電信設(shè)備和其它便攜式應(yīng)用中的欠壓狀況的新型微處理器監(jiān)控電路,擴(kuò)充了其監(jiān)控 IC 系列。ADM6326 、ADM6328、ADM6346? 和 ADM6348? 監(jiān)控電路只需500nA 的超低供電電流,從而延長(zhǎng)了移動(dòng)裝置的電池續(xù)航時(shí)間。這些新型電路可為 DSP、ASIC、FPGA 和其它處理器電源的精密監(jiān)控提供低功耗選擇方案,以檢測(cè)可能導(dǎo)致系統(tǒng)故障的欠壓狀況。這些監(jiān)控 IC 可以監(jiān)控2.5V、3V、3.3V 和5V 電壓軌。ADM6326、ADM

- 關(guān)鍵字: ADI 監(jiān)控電路 監(jiān)控IC DSP ASIC FPGA

FPGA平臺(tái)漸成系統(tǒng)核心

- 今天,F(xiàn)PGA已經(jīng)被應(yīng)用于系統(tǒng)的核心。無(wú)論是用來(lái)完成關(guān)鍵功能還是直接作為系統(tǒng)核心,今天的FPGA所提供的性能、功耗和容量都已經(jīng)達(dá)到甚至超過(guò)此前ASIC或ASSP的水平。 25年前,賽靈思公司共同創(chuàng)始人之一 Ross Freeman發(fā)明了FPGA(現(xiàn)場(chǎng)可編 程門(mén)陣列),僅憑一項(xiàng)專(zhuān)利,Ross就激發(fā)了一個(gè)行業(yè)的創(chuàng)新熱情。 很多電子設(shè)計(jì)師認(rèn)為,F(xiàn)GPA將是21世紀(jì)最重要的集成電路技術(shù)之一,而傳統(tǒng)門(mén)陣列和結(jié)構(gòu)陣列技術(shù)將退居到特殊的大批量應(yīng)用。在FPGA誕生之初,可編程邏輯主要用于系統(tǒng)外圍,作

- 關(guān)鍵字: 賽靈思 FPGA ASIC ASSP

SoC原型驗(yàn)證領(lǐng)域FPGA應(yīng)用逐年增加

- 近幾年來(lái),F(xiàn)PGA在驗(yàn)證SoC設(shè)計(jì)上的應(yīng)用發(fā)展非常迅速,這是因?yàn)殡S著半導(dǎo)體設(shè)計(jì)、制造工藝越來(lái)越先進(jìn),SoC、ASIC設(shè)計(jì)的規(guī)模變得越來(lái)越大,只采用傳統(tǒng)軟件仿真的方式,已經(jīng)不能夠充分地驗(yàn)證功能。另外,大量的前期軟件開(kāi)發(fā)也需要一個(gè)接近SoC、ASIC設(shè)計(jì)的硬件原型。而采用FPGA來(lái)模擬芯片設(shè)計(jì)的原型,已被證明是最有效、最經(jīng)濟(jì)的方式。目前,用于 SoC原型驗(yàn)證的FPGA銷(xiāo)售額已增加到整個(gè)FPGA銷(xiāo)售的7%~9%,相信這一比例還將逐年提高。 SoC原型應(yīng)用對(duì)FPGA有一定的需求。比如規(guī)模通常需要比較大,

- 關(guān)鍵字: FPGA SoC ASIC

asic ip核介紹

您好,目前還沒(méi)有人創(chuàng)建詞條asic ip核!

歡迎您創(chuàng)建該詞條,闡述對(duì)asic ip核的理解,并與今后在此搜索asic ip核的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對(duì)asic ip核的理解,并與今后在此搜索asic ip核的朋友們分享。 創(chuàng)建詞條

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會(huì)員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢(xún)有限公司

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢(xún)有限公司