多路同步串口的FPGA傳輸實現(xiàn)

當接收模塊有請求時,發(fā)送模塊即將接收模塊采集到的數(shù)據(jù)寫入發(fā)送模塊的緩存FIFO中,將其稱之為S_FIFO。每輪從R_FIFO中傳輸?shù)?個數(shù)據(jù)均依次存入S_FIFO中。

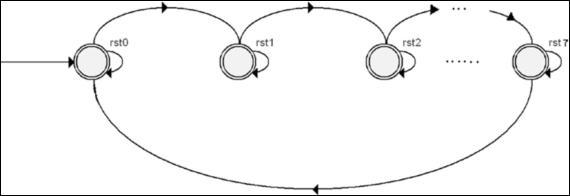

本文引用地址:http://www.104case.com/article/94602.htm因為DSP的8個同步串口均同時工作,可以認為當有一個輸入模塊的數(shù)據(jù)接收完畢時, 8個端口的數(shù)據(jù)均應(yīng)該接收完畢,保險起見,可以延時若干時鐘周期后開始接收數(shù)據(jù)。從端口0至端口7為一輪,若此時有端口沒有數(shù)據(jù),即可認為此端口暫無數(shù)據(jù)輸出,用數(shù)據(jù)0替代,發(fā)送模塊繼續(xù)接收下一個端口的數(shù)據(jù)。用狀態(tài)機來實現(xiàn)此功能,如圖4所示。

圖4 S_FIFO寫操作的狀態(tài)機圖

發(fā)送模塊完成FPGA向ARM的數(shù)據(jù)傳輸,當FPGA發(fā)送模塊S_FIFO中的數(shù)據(jù)達到一定數(shù)量時,FPGA即向ARM發(fā)出發(fā)送數(shù)據(jù)請求,ARM即開始對FPGA進行數(shù)據(jù)的讀取。

FPGA中的S_FIFO同樣也是異步FIFO。寫時鐘由鎖相環(huán)提供100MHz;讀時鐘由ARM的讀取使能信號OE取反得到,讀使能由ARM的片選信號NGCS取反得到。ARM讀取數(shù)據(jù)會產(chǎn)生NGCS與OE低電平信號,無操作時置高。每次讀取數(shù)據(jù)時NGCS與OE先后置低,取反接至S_FIFO讀端口分別為NGCS_N與OE_N。對S_FIFO讀取時,每當讀時鐘OE_N為上升沿,讀使能NGCS_N必為1,完成一次讀取操作。

這樣實現(xiàn)了ARM與FPGA之間的跨時鐘域數(shù)據(jù)傳輸。FPGA發(fā)送數(shù)據(jù)采取乒乓操作, ARM可以源源不斷的將S_FIFO中的數(shù)據(jù)讀取出來。FPGA和ARM的數(shù)據(jù)傳輸原理圖如圖5所示。

評論