多路同步串口的FPGA傳輸實現(xiàn)

FPGA內(nèi)部采用異步FIFO解決DSP時鐘頻率和FPGA時鐘頻率不匹配的問題,寫時鐘由DSP輸出的同步時鐘信號提供,時鐘頻率為60MHz;讀時鐘由FPGA的鎖相環(huán)PLL時鐘提供,PLL輸出時鐘頻率為100MHz。

本文引用地址:http://www.104case.com/article/94602.htm接收模塊

由于DSP的8個同步串口同時寫入,F(xiàn)PGA數(shù)據(jù)接收模塊一共有8個,每個模塊接收到的數(shù)據(jù)都存放在一個特定的FIFO中,將其稱之為R_FIFO。

DSP輸出信號為frame,clk, data,F(xiàn)PGA以DSP同步串口的輸出時鐘clk作為采集數(shù)據(jù)的時鐘。系統(tǒng)上電結(jié)束后,F(xiàn)PGA等待ARM發(fā)送接收允許指令,接收允許后,F(xiàn)PGA就可以開始接收數(shù)據(jù)。

當frame信號為高,F(xiàn)PGA即開始接收從DSP發(fā)送的串行數(shù)據(jù),在每個dsp_clk的上升沿讀取一個bit的數(shù)據(jù),之后將數(shù)據(jù)轉(zhuǎn)入移位寄存器中。FPGA引入一個模塊,時刻監(jiān)測frame的下降沿,當frame下降時,即表示一個字的數(shù)據(jù)發(fā)送完畢,移位寄存器的數(shù)據(jù)放入R_FIFO的數(shù)據(jù)輸入口,將R_FIFO的寫使能置高,向R_FIFO發(fā)出寫入請求,寫入此時的數(shù)據(jù)至R_FIFO中,依次循環(huán)。當R_FIFO中的數(shù)據(jù)個數(shù)不為0時,即向FPGA的發(fā)送模塊發(fā)送請求。

發(fā)送模塊

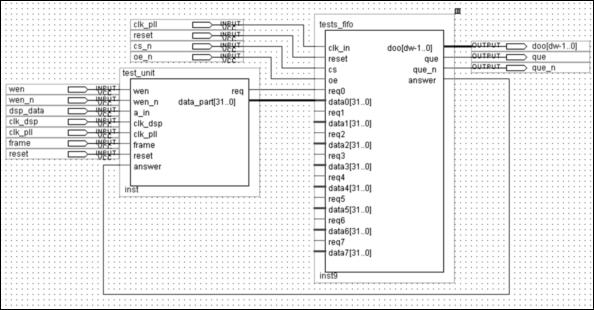

接收模塊接收到DSP同步串口數(shù)據(jù)后,即通過reg與answer信號與FPGA數(shù)據(jù)發(fā)送模塊之間進行數(shù)據(jù)傳輸,如圖3所示。

圖3 FPGA接收及發(fā)送模塊

評論