邊界掃描與處理器仿真測試(05-100)

當前,PCB是越來越復(fù)雜,不言而喻,想要獲得滿意的測試覆蓋范圍也更困難了。而且每種測試方法都有其固有的局限性。于是,測試工程師們不得不另辟蹊徑,將幾種技術(shù)組合起來以達到他們所要求的測試覆蓋范圍。這正是IEEE 1149.1邊界掃描(俗稱JTAG)和微處理器仿真測試所追求的。邊界掃描和處理器基仿真測試有各自的應(yīng)用領(lǐng)域,每種技術(shù)都能達到某種程度的測試覆蓋范圍。然而將兩種技術(shù)無縫地組合在一起,就有可能達到更高的總測試覆蓋范圍,是任何一種單獨技術(shù)無法比擬的。

本文引用地址:http://www.104case.com/article/91570.htm若將傳統(tǒng)的JTAG結(jié)構(gòu)性測試和處理器基功能仿真測試組合起來,提高了測試覆蓋范圍,從而可以簡化測試,簡化程度取決于所采用的其它測試方法,如電路內(nèi)測試(ICT)、自動光學檢查(AOT)、或飛行探針法。確實,即便工程上存在缺陷,如電路板上不合適的可測試性設(shè)計(DFT)性能等,也可以得到一定程度的彌補。

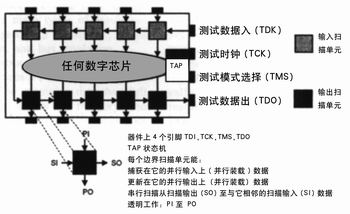

符合IEEE1149.1邊界掃描標準的半導體器件,在器件四周有一組串行移位寄存器,邊界掃描這個術(shù)語因此得名。在邊界掃描芯片上,每個主輸入信號和主輸出信號都設(shè)置有一個稱為邊界掃描單元的多用途存儲單元(圖1).

圖1 帶邊界掃描單元半導體器件的方框圖

在PCB設(shè)計上,將各個芯片的邊界掃描單元串接成并行輸入,并行輸出的移位寄存器。數(shù)據(jù)可在每個邊界掃描單元的輸入、輸出上捕獲,或串行地掃描通過整個單元鏈。這個鏈路稱為邊界掃描路徑,或簡稱為掃描路徑。

評論