基于PCI總線數(shù)字信號處理機的硬件設計(05-100)

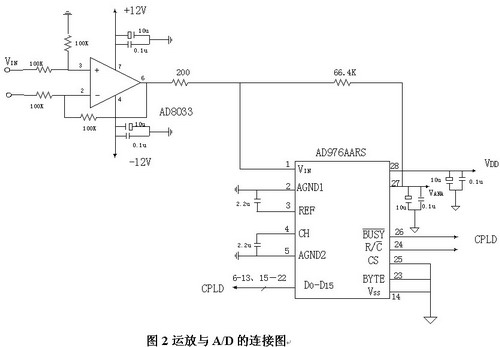

可直接接運放AD8033輸出,其中AD8033是低功耗、高精度的運放,這里接成跟隨器模式。轉換時鐘由CPLD給出(R/C)信號,CPLD轉接DSP1的TMR0E,并倒相后形成R/C信號,這樣,數(shù)據(jù)采集的周期由DSP的定時器控制,可以實現(xiàn)周期可調的。又將AD976AARS的BUSY信號引入到CPLD,用于鎖存A/D轉換數(shù)據(jù)。運放與A/D的電路結構如圖2:

本文引用地址:http://www.104case.com/article/91451.htm

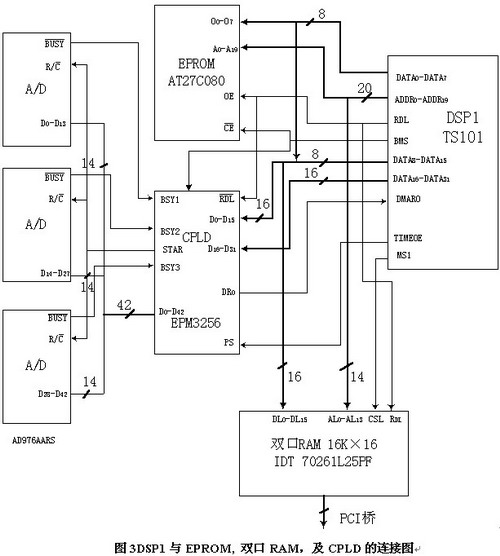

系統(tǒng)采用1片CPLD(EMP3256)作A/D轉換輸入數(shù)據(jù)鎖存、產生DSP所需的復位信號等。同時,CPLD還要完成PCI橋的一些控制信號的生成、轉接。實際上也就是作為PCI局部總線的仲裁器,它對PCI接口芯片和DSP提出的占用局部總線的請求進行仲裁,協(xié)調它們之間的邏輯關系,使局部總線上的操作順利進行。系統(tǒng)還采用了兩片16K×16位的雙口RAMIDT70V261來構成DSP信號處理機與PCI的接口,其中RAM1作數(shù)據(jù)輸入,RAM2作數(shù)據(jù)輸出。

PCI橋采用PCI9054完成,PCI9054是PLXTechnology公司的較新產品,是一低成本,低功耗,功能較強的PCI橋芯片,可以連接PC機的PCI總線和局部總線,是先進的PCII/O加速器,采用了先進的PLX數(shù)據(jù)流水線結構技術,是32位、33MHz的PCI總線主I/O加速器;符合PCI本地總線規(guī)范2.2版,有M、C、J三種模式;針對不同的處理器及局總線特性可選,盡量減少中間邏輯;具有可選的串行E2PROM接口,本地總線時鐘可和PCI時鐘異步。PC9054內部有6種可編程的FIFO,以實現(xiàn)零等待突發(fā)傳輸及本地總線和PCI總線之間的異步操作;支持主模式、從模式、DMA傳輸方式,因其強大的功能可應用于適配卡和嵌入式系統(tǒng)中。但由于DSP沒有提供直接與PCI9054接口的引腳,故采用雙口RAM作數(shù)據(jù)緩沖,其優(yōu)點是不必改造PCI產生信號以適應DSP的要求。時序配置上較為容易。同時,分開設置的輸出輸入通道,也方便了用戶的應用。

DSP1與EPROM,雙口RAM,及CPLD連接如圖3:

評論