MPF 2008: 混合架構主宰消費類領域

同構架構已經兌現了其承諾:有效的低功耗、靈活性以及準備好應對任何新的工作負荷,加上在互聯網上升級消費電子系統的好處。然而,在日本舉行的2008年微處理器論壇(MPF)上,為期兩天的日程上填滿了24個演講,其中,兩個是主題演講,除了軟件工具之外,只有一個演講可能聲稱描述同構架構設計。

本文引用地址:http://www.104case.com/article/89405.htm各個公司提交的異構(heterogeneous)設計存在差異,但是,它們有一點是共同點:它們并不是由節省功率而展示的高度并行的同構架構。更為精確地說,把在一顆芯片上的四顆處理器視為構成一種高度并行同構架構是不公平的。然而,即使一顆芯片寬大地把它們包含在一類中,在2008年日本MPF上,所展示的大多數四引擎同核實現均采用與硬線連接的加速器接口掛鉤來實現的,而不是增加更多的相同的ISA核,以便不需要特殊目的引擎就完成任務。

豐富的配置

根據處理通用目的控制工作負載所采用的配置以及所實現的針對特定應用的加速方法,在2008日本MPF上所展示的架構可以分為幾類。

在混合架構設計中,控制引擎由作為一個多核處理器工作的若干通用目的內核實現或僅僅由一個內核實現。引擎可接受的功耗取決于執行通用目的應用以及控制不同的音視頻編解碼器所需要的性能。一般來說,處理器必須有效率,但是,所需要的效率范圍進一步依賴于功率的可用性。在起居室中的多媒體應用的要求可能更為寬松,而安裝在汽車中的系統將期待更佳的效率。蜂窩電話和其它電池供電的手持設備將被設計為消耗最低的功率。

加速器的設計可以采用幾類實現方案,從采用定制指令集架構(ISA)的內核、參數受控的靈活狀態機到固定程序硬件連線的實現。根據在控制處理器以及加速器之間是否需要去掉存儲器訪問,可能要或不要提供本地存儲器。

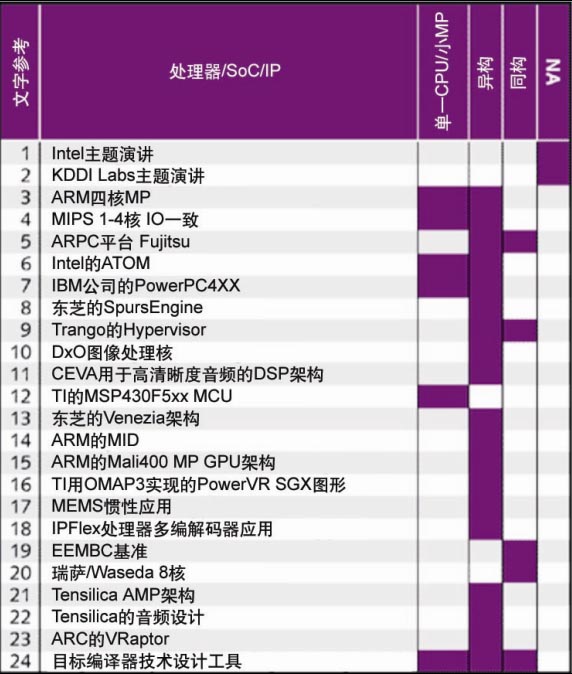

架構設計的分配

架構配置的分配結果是不言而喻的(表1)。在表1中,“Text Reference”一列指的是對表中列出的有限陳述的簡短描述;這些陳述由描述每一個陳述的加括弧的數字來識別。

表1:對于在器件的實現中所采用的架構類別來說,通過表中的各欄可以識別在2008日本MPF上展示的最佳匹配的處理器/SoC/IP。處理器的標題為縮寫。參考數字可以被用來查找陳述的簡短描述。軟件已經被包含以實現完備性,但是并不總是顯示硬件的存在。

為了公平起見,我們已經省略了兩個可能顯示異構芯片的主題演講,但是,并不是如此明確。會議的背景集中在娛樂之處,并且暗指需要不同的架構配置,這些配置由英特爾公司的副總裁、數字娛樂組的Ton Steenman以及KDDI Labs公司的執行總監Hiroki Horiuchi做了適當的設置。他們的演講在描述不久將受到歡迎的連接固定和移動設備(Ton Steenman) [1]的世界上相互補充,而網絡和無線電意味著[2]保持它們的工作(Hiroki Horiuchi)。我們還省略了四個重點放在軟件的演講;我們發現在18個新的設計中,17個不是同構設計。我們還發現,所介紹的大多數軟件工具重點放在基準上,并提供對同構架構的并行支持。

從統計上看,采用24個演講作為樣本就得出關于一個覆蓋全球人口的平均數的結論是不準確的,除非已知這個樣本代表可靠的覆蓋率。考慮那些已經在2008日本MPF上做演講的公司,我們能夠假設它們大部分代表了IP、處理器以及復雜SoC設計的領導者。如上所述,這一統計數字說明,我們試圖解釋的狀況出自如此高度偏向有利于異構架構的樣本。

在大批量銷售的消費娛樂芯片中,有三個較之于其它應用更為重要的參數:(1) 流片投資;(2) 在并行化編譯器上缺乏突破;(3) 進展緩慢的音視頻標準。

根據作者的感覺,表2示出了對實現技術的、總是有幫助但可能引起爭議的定性比較。數字代表分析師的定性估計而不是精確的數據。數字越小則越好。

表2:該表格根據作者的感覺對各種實現技術進行了定性比較。數字越小越好。在價格敏感的應用中,并行同構架構表現不那么好。異構架構將需要重新說明,只要新的編解碼器看起來不能由控制加強的內核執行的話。然而,這些將在每幾代出現一次,并且大多數的硬連線或定制ISA單元仍將是可重用的。

并行同構實現根據整個比較參數被給予一個平均打分,因為這些實現在靈活性、降低開發風險、遠程診斷或升級上較之于異構架構更好。然而,它們在流片投資以及—更為重要的是—軟件工具上落后于其它架構。

最佳打分仍然看起來屬于單核或四核、“高頻”實現。這個配置將繼續被使用,只要運行應用所需要的性能能夠允許芯片的功耗被保持在控制之中。

對于批量銷售來說,兩個異構是最佳的。流片投資低,使得裸片價格在消費應用中有競爭力。開發風險高,因為它意味著要采用ASIC設計且所得到的芯片具有較低的編程靈活性,然而,如果它導致非常高的營業收入就非常值得投資。附加的優勢是在定制ISA和硬線編解碼器上:標準進化緩慢。設計工程師能夠重用定制ISA以及在許多芯片中的硬線加速器。

芯片和內核被隨意連接至加速器

相當多的演講提供了具有或不具有加速器的、采用一個小型MP群的選擇權。由ARM公司高級編程經理John Goodacre講述的四核MP配置采用了該公司最新的Cortex-A9,它可能被認為是一種混合架構,因為它通過其NEON協處理器提供DSP處理。然而,ARM還實現了一種連接,通過它多個處理器群能夠與定制設計的加速器配合工作。MIPS技術公司的高級工程師Tom Berg介紹了在多線程處理器中的IO一致性,解決了一種類似的MP配置。它能夠在SoC中采用該公司的1~4MP核,從而把通用目的處理與調諧器、解碼器以及圖形加速器一起集成進混合架構的實現之中。

Fujitsu Laboratories的演講由Processing LSI Development Group總監Atsuhiro Suga提供。Atsuhiro Suga在2007年日本MPF上就因他的軟件演講而知名。在那時候,他介紹了一種被用于在多個處理器之間分配任務的異步遠程程序調用(ARPC)的應用,它與那些不必在相同的ISA上實現的引擎集合起來(見MPR 8/13/07-01, “Fujitsu Calls Asynchronously”一文)。Suga的新演講[5]描述了增加的一種硬件狀態機,以替代可能相同的處理器之一,迄今為止,這項任務利用有待狀態機處理的工作負荷的線程進行調度。

英特爾公司的首席架構師Belli Kuttanna介紹了它的Atom芯片,不久前,該公司宣布它已經進入復雜的采用多種設計的SoC市場,其中一些是基于雙線程Atom架構。一個這樣的SoC設計把計算復雜體與媒體加速器結合起來,實現圖形、音視頻以及顯示器引擎,還允許第三方知識產權被連接起來。Atom芯片連接可以隨意接上加速器的處理器組,它們是完全或部分可編程的。

IBM公司的顧問研發工程師Masahiro Murakami講述了IBM的PowerPC4xx SoC平臺[7],描述了允許把用戶定制邏輯連接至PowerPC內核以創造多核異構設計的接口裝置。這種至PowerPC內核的連接性是通過把連接內核的本地總線橋接至AHB總線來實現的。在以前的單一或異構配置的PowerPC設計中,如Cell BE,可以成為高度集成的SoC的控制器。

異構架構

東芝負責蜂窩項目的項目帶頭人Yoshio Masubuchi演講了該公司的SpursEngine [8],并且是該公司領導該芯片開發的邏輯選擇。 SpursEngine的設計結合了來自8-SPE Cell BE的四個增效處理器單元(SPE),加上支持不同視頻編解碼器的硬件加速器。

Trango Japan公司的領導Tom Kobayashi講述了面向DRM的安全執行環境的實現。Kobayashi描述了Trango的系統管理程序的安全軟件域的應用。Trango的系統管理程序在一個或多個操作系統以及基礎硬件之間形成一種抽象層。它能夠把一個或多個處理器分為獨立安全和針對應用執行的域。處理器本身可以是相同的或者可以作為混合架構被實現。

DxO Labs的首席運營官Bruno Liege講述了一種可配置、可編程、面向像素的、高質量、高性能、可授權的IP架構[10],它被設計為一種把窄數據路徑、12-bit標量引擎級與寬向量處理級相結合的加速器。多個ALU結構由采用ARM的AHB總線的內核中的標量邏輯進行控制。

CEVA公司的核心架構總監Michael Boukaya的演講與在消費娛樂中缺乏成功的高度并行引擎的許多其它實現相比,更為讓人大開眼界。CEVA的32-bit DSP單一引擎所獲得的性能是通過在DSP內核上采用高頻,加上用于專用函數如FFT和維特比的加速器來實現的。

德州儀器(TI)的超低功耗MSP430F5xx MCU家族[12]由MSP430 MCU首席架構師Horst Diewald講述,它利用在性能上的提升進一步提供超低功耗控制。Horst描述了通過硬件和軟件相結合來管理處理器,以實現諸如遠程抄表、對用于安全目的的氣體泄漏的檢測、個人醫療以及能量收集等功能所要求的低功耗數字。新家族的芯片增加了一體化外設,如射頻、加密以及至MSP430平臺的LCD接口。

東芝的首席專家Takashi Miyamori介紹的Venezia架構[13]能夠利用由用戶選擇的主CPU—如ARM或MIPS—實現一種控制資源,加上由不同的處理器—如控制和線程的分派所需要的—實現的加速Venezia引擎,一個調度器,以及一些媒體處理引擎。

ARM公司的研發組咨詢工程師Nigel Paver描述了移動互聯網設備(MID)[14]可配備內部處理資源的途徑。根據Paver的介紹,高性能的MID能夠利用由高端攝像機圖像處理器、三維圖形引擎、高清視頻編解碼加速器、TrustZone安全性以及包含GPS基帶功能的、支持的Cortex Aclass內核來實現的異構架構。稍廉價的較低性能MID還可以由TrustZone實現加密。MID可以由ARM11內核控制。它可以配合較低性能的攝像機、非高清視頻編解碼器、不太先進的三維圖形以及一體化的無線基帶。

此外,ARM公司的高級產品經理Chris Porthouse講述了Mali400 MP GPU架構[15],其用途是與ARM CPU內核在同一芯片上工作。Mali-400 Vertex處理器以及多達四個片段處理器被通過本地互連連接至MaliMMU。MaliMMU被連接至一個L2高速緩沖存儲器,它本身接至AXI總線。ARM公司的一部APB外設總線被用于把數據傳輸至Vertex和片段處理器以及至MaliMMU和L2高速緩沖存儲器。

TI公司的圖形軟件工程師Clay D. Montgomery講述了由OMAP3家族之一的OMAP35x應用處理器所采用的圖形內核[16]。TI在OMAP3530高集成度處理器中正采用由Imagination Technologies提供的異構PowerVR SGX圖形內核。該芯片還集成了一種TMS320C64x+ DSP內核,加上圖形外設以及加速器。異構OMAP35x平臺以Cortex-A8內核為基礎。

ADI日本公司微機電技術組總監Yutaka Katano以及In-Stat技術分析師Max Baron講述了一種泛系統的異構架構[17],采用了DSP處理器、MEMS、運算放大器以及連接至桌面的藍牙接口。

SATO創始人Tomoyoshi與IPFlex首席技術官IPFlex介紹了一種異構架構[18],它采用大量不同的功能處理單元(PE)以及能夠更加有效地處理MPEG-2/-4和H.264比特流的增強比特流處理器(BSP)。

PE和BSP單元能夠被動態地重新配置以執行在前景中的各種任務,與此同時,通過從外部存儲器加載下一個配置信息而在背景中設置新的任務。盡管它具有靈活性,IPFlex公司的新引擎能夠執行多個編解碼器的應用,這一功能在產品發布之后會加入設計中,它還能夠被配置為執行針對用戶的工作負荷。

同構架構

日本嵌入式微處理器基準聯盟(EEMBC)的區域經理Satoshi Otsuka講述了面向多個內核以及高度并行同構架構的基準狀況。對于MPR了解的最佳情況來說,該聯盟仍然就針對采用相同內核進行配置的最初套件進行最終完善。瑞薩公司提供且由日本Waseda大學開發的高性能并行化編譯器所支持的一種8個CPU的多核處理器[20],被認為應該考慮為同構架構。Waseda大學的教授Hironori Kasahara以及瑞薩科技公司的部門經理Toshihiro Hattori輪流介紹了OSCAR編譯器以及多核架構。

同構可配置、可擴展處理器

Tensilica公司的技術福音傳道者Steve Leibson描述了可擴展配置的優點,他認為,對稱多處理器(SMP)架構對于服務器不錯,但是,在多媒體應用中的運行效率不高。Tensilica的方法就是采用在公司的基本Xtensa架構上實現的針對應用的ISA[21]來創建加速器。異構架構—如在愛普生打印機中所采用的—被用于描述這類加速器的應用。

Tensilica公司的Darin Petkov介紹了一種音頻設計,它采用了由ISA擴展獲得的應用專用處理器[22],在該公司的Xtensa LX VLIW基本引擎上構建了大約300個針對音頻的指令。

ARC公司的首席技術官Nigel Topham介紹了該公司采用異構架構實現的VRaptor家族[23],其中有采用ARC 750D CPU針對工作負荷而配置的可編程加速器。該公司在控制它的流以及計算群的協調群中采用了類似的CPU,它們本身作為異構架構被實現。

Target Compiler Technologies公司的首席執行官Gert Goossens講述了該公司的工具,它們有助于設計工程師創建針對應用的處理器(ASIP)[24]以及從零做起的編程工具。與采用所有其它的針對應用的引擎一樣,一組ASIP內核可以被最優化以提供具有最少邏輯的SoC以及對工作負荷的良好分配,唯一的例外就是基本狀態機或也是從零開始設計的簡單的處理器,從直覺上看,在流片投資以及功耗上提供優勢,而所付出的代價就是設計一種品牌新架構所需要的額外工程時間。

本文總結

與多核同構配置相比,異構架構提供有利于流片投資以及功耗的更佳折中。回顧過去可見,在流片投資、功耗以及軟件創建上同構架構要變得更為舒適,設計工程師必須看到用于相同ISA內核的更多優勢。

目前,同構架構的狀況使之更加適合于高度數據密集的處理工作。對于家庭娛樂以及移動應用來說,在一個量產芯片的設計工程師的喜好中,同構架構僅僅高于FPGA。同構配置將在面向即將出現的應用—如專用圖形、游戲和汽車視頻圖像識別—中獲得優先權。

同構架構在低成本、大批量應用中獲得競爭力以前,硬線連接以及針對應用的內核IP提供商將有機會贏得市場占有率。

評論