利用AMSVF進行混合信號SoC的全芯片驗證

自動總線連接

本文引用地址:http://www.104case.com/article/85650.htm在HDL語言中,總線信號的使用非常普遍且不可或缺。但SPICE中并沒有類似的概念或定義,連接到SPICE支電路的Verilog總線必須被分解到每一個單獨的端口,而且必須按順序連接。例如:

module verilog;

wire [0:5] v;

analog_top xana_top ( v[0], v[1], v[2], v[3], v[4], v[5] );

endmodule

.subckt analog_top p<0> p<1> p<2> p<3> p<4> p<5>

...

.ends

為了準確地連接Verilog實例和SPICE subckt,總線信號v[0:5]必須被分離。通常,分離的過程需要極為耗時的手動編輯,尤其對于規模較大的總線更是如此。而在AMSVF中,通過自動總線連接功能,用戶可以輕松地將實例寫為:

analog_top xana_top ( v );

用戶可以在SPICE網表中設置總線界定符,告知AMSVF哪個符號用于總線信號。這里符號<> 和[ ]為默認界定符,甚至也可以支持空總線界定符。

AICM與BDR

AMS Designer嚴格遵從Verilog AMS的規范確定(Discipline Resolution)過程,它讓用戶可以依靠工具確認信號間的連通性,并能實現連接模塊的自動插入。

AICM(自動插入連接模塊)算法判定通過未聲明端口相連的線網規范,然后在模擬和數字域邊界上插入連接模塊。除了電氣到邏輯(E2L)以及邏輯到電氣(L2E)這兩個普通的連接模塊外,AICM還支持雙向的連接模塊,這對于不想明確指定線網端口方向的用戶來說是非常方便的。

在驗證大規模設計時,尤其是在ncelab階段,新的BDR(鎖定規范確定)功能能夠讓設計師應用他們的設計知識去控制并縮小規范確定的解析范圍以提升性能。此外,如果通過AMSVF驗證的設計在數字和模擬之間有清晰的界限,或其所有線網都已被明確地聲明,那么,利用“-disres none”選項甚至可以跳過規范確定過程,顯著縮短運行時間。因此,這種新功能可以大幅提高AMSVF在ncelab階段的性能和效率。

此外,BDR對于多電源設計來說是非常實用的。例如,對于同時使用5V、3.3V和1.8V供應電源的電路來說,當數字模塊用不同的供應電源連接模擬模塊時,數字信號將會有不同的數字規范,如logic5V、logic33V 和logic18V,而對于單電源設計來說,僅用缺省的logic這一個數字規范即可。因此通過這種功能,用戶可以為設計中的數字模塊設定不同的數字規范,以便模擬器更加準確地插入連接模塊。

Stub View

Stub View提供了從模擬中移除原理圖或Verilog AMS模塊的途徑。通過移除不影響模擬結果或是沒有使用到的模塊,可以幫助用戶加快模擬速度。另外,該功能可以用于確認哪個模塊是造成模擬速度降低的主要原因。

比如,電路中包含有不同激勵源的3個通道,每個通道彼此獨立,利用Stub View功能移除其中的一或兩個通道,就可以大幅加快模擬速度。

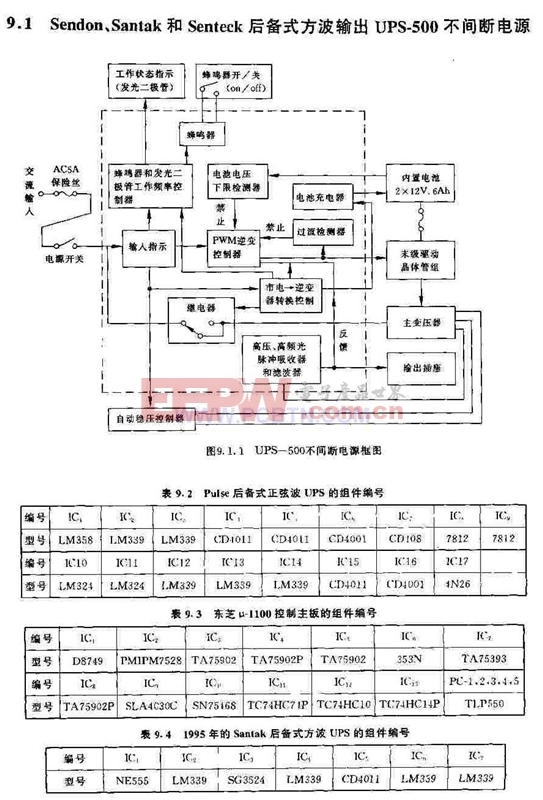

UPS求解器

一般來說,電源/地線網絡中存在大量的寄生RC,在版圖后仿真時,這些寄生RC將會大大降低性能,并侵占大量內存。對于這類模擬,AMSVF中的UPS求解器可被用于加速模擬速度,同時保持精確性。模擬器首先偵測電源網絡,然后將整個設計分離為電源網絡和信號網絡兩部分。電源網絡部分由UPS求解器處理,而信號網絡部分則由Ultrasim求解器處理。電源網絡模擬的示意圖如圖2所示。

圖2 電力網絡模擬法示意圖

使用傳統的瞬態模擬和UPS求解器分別進行電壓降分析的性能對比如表1所示。

VR技術

由于芯片內電源電壓不斷降低,并開始采用多電源電壓,因此,越來越多的混合信號/RF或數字電路均使用片上穩壓器來產生內部供電電壓。Ultrasim求解器通過有效的分區技術實現模擬加速,但這只能應用在電路由理想電源電壓驅動的情況下。使用傳統的分區技術,所有連接到內部穩壓源的模塊都必須包含在單個分區內,嚴重影響了模擬速度。

VR(穩壓)技術能夠克服這種限制, 讓用戶能夠方便地對由內部穩壓器供電的電路模塊進行模擬仿真。

快速包絡分析

總的來說,當被調制電路采用傳統的瞬態分析時,需要非常小的時間步長以適應高頻載波信號,并且需要長時間的持續周期覆蓋低頻基帶信號,這將使得模擬變得非常緩慢和困難。快速包絡分析主要用于解決這個難題,這些電路類型通常出現在發射器、接收器等RF電路中。

評論