利用SmartCompile和賽靈思的設(shè)計(jì)工具進(jìn)行設(shè)計(jì)保存(07-100)

Synplify把時(shí)間戳寫入到EDIF,它可用于確定每一個(gè)編輯點(diǎn)自上一次的布局和布線運(yùn)行后是否發(fā)生改變。一份tcl文件也由Synplify 寫入,從而為賽靈思布局和布線定義分區(qū)。當(dāng)用戶指定“syn_hier=locked,physical”時(shí), Synplify把額外屬性寫入 EDIF之中,要觀察的內(nèi)容包括該模塊最近被綜合時(shí)的時(shí)間戳。如果從上一次運(yùn)行開始模塊一直沒有發(fā)生變化,舊的時(shí)間戳被存入EDIF之中。每個(gè)標(biāo)有“locked, physical”的編輯點(diǎn)將含有這樣一個(gè)時(shí)間戳。賽靈思ISE 9.1i 拾取該時(shí)間戳,與以前的布局和布線時(shí)間戳進(jìn)行比較,并且只在發(fā)生改變的模塊上進(jìn)行增量布局和布線。

總結(jié)和優(yōu)點(diǎn)

一般說來,保存一項(xiàng)設(shè)計(jì)要比重新實(shí)現(xiàn)一項(xiàng)設(shè)計(jì)更快。因此,如果大部分設(shè)計(jì)能通過采用Partitions或SmartGuide進(jìn)行保存,實(shí)現(xiàn)這項(xiàng)設(shè)計(jì)所需的時(shí)間將會更少。在用于測試這些技術(shù)的廣泛的工具套件中平均運(yùn)行時(shí)間的改善,比最初的實(shí)現(xiàn)要快 2.5倍。例如,如果一項(xiàng)設(shè)計(jì)要花3個(gè)小時(shí)實(shí)現(xiàn),那么,利用設(shè)計(jì)保存的實(shí)現(xiàn)所需時(shí)間就要少1個(gè)小時(shí)。在一些最佳的情形下,運(yùn)行時(shí)間比最初實(shí)現(xiàn)要快到6倍之多。

設(shè)計(jì)保存的另一個(gè)優(yōu)點(diǎn)是減少了驗(yàn)證。如果一個(gè)設(shè)計(jì)模塊被嚴(yán)格地保存,那么,那部分設(shè)計(jì)在設(shè)計(jì)修改后就不需要再重新驗(yàn)證。因?yàn)橐驯4娴膶?shí)現(xiàn)與前一次的實(shí)現(xiàn)是完全相同的,布局、布線和時(shí)序是相同的,這樣重新驗(yàn)證就沒有必要了。

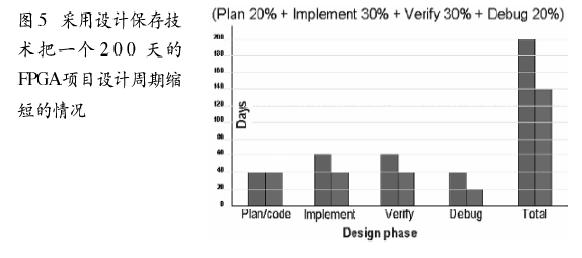

要花大約200天來實(shí)現(xiàn)的FPGA設(shè)計(jì)通常涉及設(shè)計(jì)定義、實(shí)現(xiàn)、驗(yàn)證和調(diào)試。分配到每個(gè)階段的預(yù)計(jì)時(shí)間如圖5所示。采用設(shè)計(jì)保存技術(shù),就有可能使解決問題所花費(fèi)的時(shí)間減少幾個(gè)月。這是基于這樣的假定:FPGA 的實(shí)現(xiàn)時(shí)間是幾個(gè)小時(shí),因此,運(yùn)行時(shí)間可能被減少。它還假定該設(shè)計(jì)采用基于模塊的驗(yàn)證測試基準(zhǔn),因此,在該設(shè)計(jì)內(nèi)已保存的模塊不需要被重新驗(yàn)證。如果一項(xiàng)設(shè)計(jì)采用了這種技術(shù),采用SmartCompile技術(shù)獲得解決方案所花費(fèi)的時(shí)間就被大幅縮短。

評論