利用SmartCompile和賽靈思的設(shè)計(jì)工具進(jìn)行設(shè)計(jì)保存(07-100)

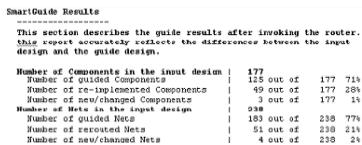

有關(guān)元器件和網(wǎng)絡(luò)的詳細(xì)信息被存儲(chǔ)在引導(dǎo)報(bào)告文件(GRF)。該文件列出了被重新實(shí)現(xiàn)的新文件和網(wǎng)絡(luò)的名稱。

本文引用地址:http://www.104case.com/article/81756.htm大約在10次的引導(dǎo)實(shí)現(xiàn)后,建議無需引導(dǎo)就進(jìn)行重新實(shí)現(xiàn)以最優(yōu)化整個(gè)的設(shè)計(jì)。這將使得以前已被引導(dǎo)的邏輯與新的或已修改過的邏輯之間得到最優(yōu)化。

采用 Partitions

有若干策略可用于決定設(shè)計(jì)中什么邏輯模塊成為待Partition的最佳候選模塊。如果縮短運(yùn)行時(shí)間是主要的目標(biāo),要把設(shè)計(jì)分成具有類似數(shù)量邏輯的4到10個(gè)之間的Partitions。如果其中的一個(gè)Partitions被修改,其它的將被保存。因此,保存數(shù)量與設(shè)計(jì)中Partitions 的數(shù)量是成比例的。另一個(gè)策略是當(dāng)難以滿足時(shí)序約束時(shí)實(shí)例創(chuàng)建一個(gè)Partition。一旦針對(duì)這個(gè)Partition的時(shí)序約束得到滿足,即使在該P(yáng)artition外部的邏輯被修改時(shí),它也會(huì)被保存起來。

為了向設(shè)計(jì)添加更多的Partitions,存在一個(gè)逐漸減小的返回點(diǎn)。Partition接口是最優(yōu)化的障礙。如果只能通過對(duì) Partition接口最優(yōu)化來解決一個(gè)關(guān)鍵路徑或包裝問題, 那么,應(yīng)該從設(shè)計(jì)中把那個(gè)Partition消除。在Partition接口上創(chuàng)建寄存器將排除出現(xiàn)時(shí)序或包裝問題的可能性。

XST和Synplify Pro兩者都可被用詳細(xì)說明RTL Partitions。

在Partition流程中使用XST

如圖4所示,要采用XST綜合工具在ISE Project Navigator中創(chuàng)建Partitions,右擊Sources列表中的實(shí)例并選擇New Partition。從這個(gè)菜單可以修改其它的Partition屬性,如保存。

在tcl接口中創(chuàng)建Partition,要使用這條命令:

% partition new

Partitions不能用批處理命令創(chuàng)建,因?yàn)樗麄冃枰谠O(shè)計(jì)中的特定邏輯模塊上設(shè)置一種屬性。

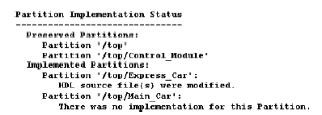

實(shí)現(xiàn)FPGA設(shè)計(jì)(XST, ngdbuild, map, par)的個(gè)別應(yīng)用生成關(guān)于哪一個(gè)Partitions在它們各自的報(bào)告文件中被保存和實(shí)現(xiàn)的信息。例如,在這個(gè)XST 綜合報(bào)告中,一些Partitions被保存,而其它的被重新實(shí)現(xiàn)。每一個(gè)已實(shí)現(xiàn)的Partition都有一個(gè)原因解釋它為什么沒有被保存。

在9.1i版本ISE中,對(duì)時(shí)序約束或命令行變更做出的修改—如努力級(jí)別—將迫使所有的Partitions被重新實(shí)現(xiàn)。

在Partition流程中采用Synplify Pro

在Synplify Pro Partition流程的情況下,用戶在運(yùn)行綜合之前,指定RTL模塊/子模塊(Partitions)作為Synplify Pro中的編譯點(diǎn)。在整個(gè)設(shè)計(jì)中運(yùn)行最初的布局和布線之后,該工具檢測(cè)哪些模塊/子模塊已經(jīng)發(fā)生了改變,并且能利用這一變化對(duì)所選擇的任意模塊執(zhí)行后續(xù)的增量布局和布線,與此同時(shí),使其它已布局/布線的模塊保持不動(dòng)。在已傳遞到布局和布線的tcl文件中,有可能詳細(xì)說明布局或布局和布線是否被保存(缺省是布局和布線)。

評(píng)論