迎接可穿戴設備時代的設計挑戰

FPGA助力節能技術

本文引用地址:http://www.104case.com/article/273934.htm在前面的幾個例子中,設計的主要目的是為了增強應用處理器本身的互連或功能。但這些基于FPGA的解決方案還提供了另一個重要的好處:使得MCU或ASSP無需同時執行一個或多個計算密集型任務,從而節省了有限的處理器資源。

但是,在許多情況下,這些設計的功耗降低具有更重要的意義。例如,圖3中的設計包含了一個硬件屏幕刷新功能,其僅需消耗傳統處理器內核所需功率的一小部分。同樣,圖4中的一些小尺寸、低功耗FPGA邏輯器件獨立于主機處理器執行圖像處理任務,這使得主機處理器大部分時間可處于節能睡眠模式。

下面探討的許多應用都使用這種節能設計方法,適用于大多數有低功耗需求的可穿戴應用。

FPGA可加速設計升級和新設計實現

可穿戴電子設備發展迅速,每一代新產品都比上一代添加了更多的功能和特性。在這些應用中,小尺寸、低成本的FPGA經常被用來擴展可穿戴式設備應用處理器的基本功能。

許多現代的微控制器都有強大的計算能力來管理傳感器和處理其產生的數據,并將它與其他數據流進行整合。但使用微控制器來完成這些工作會占用寶貴的I/O資源,并要求處理器長時間處于工作狀態,從而會影響電池壽命。

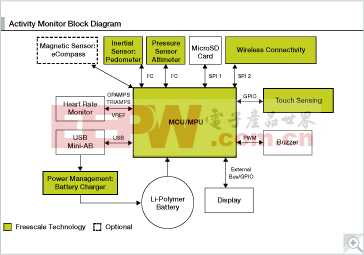

而FPGA可以用來創建半自主的I/O模塊,能夠從多個傳感器收集數據,并在沒有處理器干預的情況下完成其他高級功能。“永遠在線”的低功耗計步器采用3軸加速度計作為主要傳感器,記錄佩戴者的步數,計算所走的距離并測定燃燒的卡路里以及運動時間。

在該設計中,一些FPGA邏輯單元被配置用作加速度計的I2C接口和應用處理器SP I/O總線之間的橋接。其他的FPGA功能塊用于配置和管理加速度計。可編程邏輯也可以用于處理原始的加速度計數據,針對帶有噪聲的數據流采用統計學濾波和步數檢測算法。FPGA的另一部分功能是用來緩存得到的步數和加速度信息,直到主機處理器從低功耗睡眠狀態喚醒并收集這些數據。采用可編程邏輯內核來執行這些計算密集型任務,可使應用處理器長時間處于睡眠模式,從而有助于減少計步器的功耗。通過FPGA實現這些功能也使設計人員能夠在不影響計步器的性能和精度的情況下,使用更簡單、更低功耗的微控制器。

FPGA提供可擴展的解決方案

采用FPGA的另一個優點是,FPGA廠商通常會提供一系列類似的器件,每個器件有不同的可編程邏輯和I/O組合。使用FPGA作為ASIC的補充或替代,設計工程師可以選擇他們目前所需的邏輯門數量,開發大小合適的解決方案。

由于同一FPGA系列的器件共享參數、特性和開發資源,各種邏輯密度和I/O配置選擇使得制造商可以采取“升級時再購買”的策略,為現有的設計添加新的功能,或重組現有的功能開發新的產品。由于同一系列器件共享通用的工具鏈和IP庫,設計工程師可以迅速將升級和后續設計從設想變為產品推向市場。

總結

可穿戴設備的標準架構、功能集和專用芯片的缺失為本來就面臨緊張成本、功耗和尺寸約束的移動消費電子設計帶來了許多前所未有的挑戰。本文介紹了FPGA能夠通過一些簡單的方法幫助設計工程師解決上述問題,例如:為現有微控制器、傳感器、顯示器等之間的接口橋接,為現有的微控制器和ASSP添加新的互連和功能,以及在某些情況下提供了一種替代ASIC或SoC的選擇。

由于其靈活性、可擴展性和較低的解決方案成本,FPGA為許多類型的產品重新定義了傳統的設計周期,為設計工程師提供了許多超越傳統ASIC的優點。

評論