復(fù)位設(shè)計中出現(xiàn)的結(jié)構(gòu)性缺陷及解決方案

復(fù)位路徑的組合邏輯

1.問題(I)

如果組合邏輯輸入大約在同一時間發(fā)生變化,那么使用復(fù)位路徑中的組合邏輯可能產(chǎn)生干擾,這可能在設(shè)計中觸發(fā)虛假復(fù)位。下面是一個RTL代碼,它會在設(shè)計中意外復(fù)位。

assign module_a_rstb = !((slave_addr[7:0]==8h02 write_enable(wdata[7:0]==00))

always @(posedge clk or negedge module_rst_b)

if(!module_rst_b)data_q 00000010 ——> 00000000 ——> 01000000 ——> 01100000“生成過渡。

在這段時間里,salve_addr為“00000010”,如果wdata[7:0]始終為零且“write_enable”已經(jīng)被斷言,那么它將在module_rst_b創(chuàng)建一個無用脈沖,從而導(dǎo)致虛假復(fù)位。

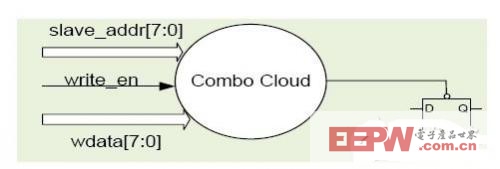

圖6:復(fù)位路徑的組合邏輯

2.解決方案

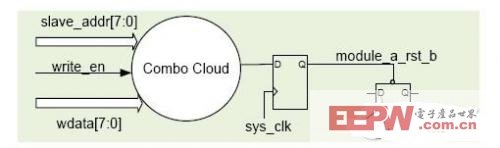

首先注冊組合輸出,然后再將其用作復(fù)位源(如圖7所示)。

圖7:復(fù)位路徑的組合邏輯解決方案

3.問題(II)

在上面的示例中,復(fù)位路徑的組合邏輯解決方案并不完善。如果組合邏輯輸入大約在同一時間發(fā)生變化,那么它可能在設(shè)計中觸發(fā)虛假復(fù)位。然而,如果組合邏輯的輸入信號變化相互排斥,那么它可能不會引起任何設(shè)計問題。例如,測試模式和功能模式相互排斥。因此復(fù)位路徑的測試復(fù)用是有效的設(shè)計實踐。

然而,對于某些情況,變化相互排斥的靜態(tài)信號或信號可能會導(dǎo)致設(shè)計出現(xiàn)虛假復(fù)位觸發(fā)。下面的示例描述了此類設(shè)計可能出現(xiàn)問題。

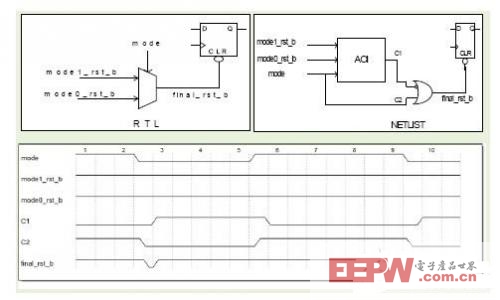

圖8:復(fù)位路徑的組合邏輯(問題2)

在上面的示例中,多路復(fù)用結(jié)構(gòu)用于復(fù)位路徑,同時進(jìn)行RTL編碼。其中“mode”是一個控制信號,不頻繁改變,而mode0_rst_b和mode_1_rst_b是兩個復(fù)位事件,然而在合成RTL時,在門控級它被分解成不同的復(fù)雜的組合(And-Or-Invert[AOI])信元。雖然在邏輯上它相當(dāng)于一個多路復(fù)用器,但由于不同的信元和凈延遲,每當(dāng)信號“mode”從1——>0變化時,final_rst_b都會產(chǎn)生干擾。

4.解決方案

*在合成過程中在復(fù)位路徑保留多路復(fù)用結(jié)構(gòu),因為多路復(fù)用結(jié)構(gòu)與其他組合邏輯相比易于產(chǎn)生干擾。MUX Pragma可以在編碼RTL時使用,這將有助于合成工具在復(fù)位路徑中保留任何多路復(fù)用器。

設(shè)計中的同步復(fù)位問題

1.問題(I)

在許多地方,設(shè)計人員在時鐘方面喜歡同步復(fù)位設(shè)計。原因可能是為了節(jié)省一些芯片面積(帶有異步復(fù)位輸入的觸發(fā)器比任何不可復(fù)位觸發(fā)器都大)或讓系統(tǒng)與時鐘完全同步,也可能有一些其他原因。對于此類設(shè)計,當(dāng)復(fù)位源被斷言時需要向設(shè)計的觸發(fā)器提供時鐘,否則,這些觸發(fā)器可能會在一段時間內(nèi)都不進(jìn)行初始化。但當(dāng)該模塊被插入一個系統(tǒng)時,系統(tǒng)設(shè)計人員可能選擇在復(fù)位階段禁用其時鐘(如果在一開始不需要激活該模塊),以節(jié)省整個系統(tǒng)的動態(tài)功耗。因此,該模塊甚至在復(fù)位去斷言后一段時間內(nèi)都不進(jìn)行初始化。如果該模塊的任何輸出直接在系統(tǒng)中使用,那么將捕獲未初始化和未知的值(X),這可能會導(dǎo)致系統(tǒng)功能故障。

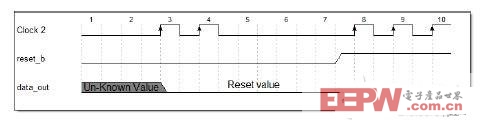

圖9:同步復(fù)位問題時序圖

2.解決方案

在復(fù)位階段啟用該模塊的時鐘且持續(xù)最短的時間,使該模塊內(nèi)的所有觸發(fā)器都在復(fù)位過程中被初始化。當(dāng)系統(tǒng)復(fù)位被去斷言時,模塊輸出不會有任何未初始化的值。

圖10:同步復(fù)位問題已解決

3. 問題(II)

在時鐘域交叉路徑使用兩個觸發(fā)同步器是常見做法。然而,有時設(shè)計人員對這些觸發(fā)器使用同步復(fù)位。相同的RTL代碼是

always @(posedge clk )

if(!sync_rst_b) begin

sync1 = 1b0; sync2 = 1b0 ;

end

else begin

sync1 = async_in; sync2 = sync1

end

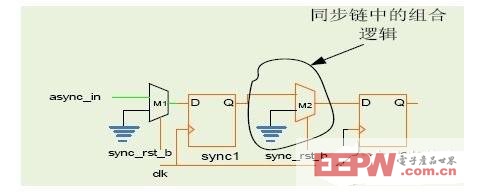

在硬件中進(jìn)行了RTL合成后,上面的代碼會在雙觸發(fā)器同步器的同步鏈中引入組合邏輯,這會帶來風(fēng)險,并縮短sync2觸發(fā)器輸入進(jìn)入亞穩(wěn)態(tài)的時間。

圖11:同步復(fù)位問題2

4. 解決方案

可用以下方式編寫RTL代碼,以避免同步鏈的組合邏輯。

always @(posedge clk )

if(!sync_rst_b) begin

sync1 = 1b0;

end

else begin

sync1 = async_in; sync2 = sync1

end

在上面的代碼中,對sync2觸發(fā)器不使用復(fù)位,因此在同步鏈中不會實現(xiàn)組合信元。然而,需要注意sync2需要一個額外的周期才能復(fù)位,這不應(yīng)導(dǎo)致設(shè)計出現(xiàn)任何問題。

評論