用電路實現(xiàn) pascal三角形運算(圖)

前言

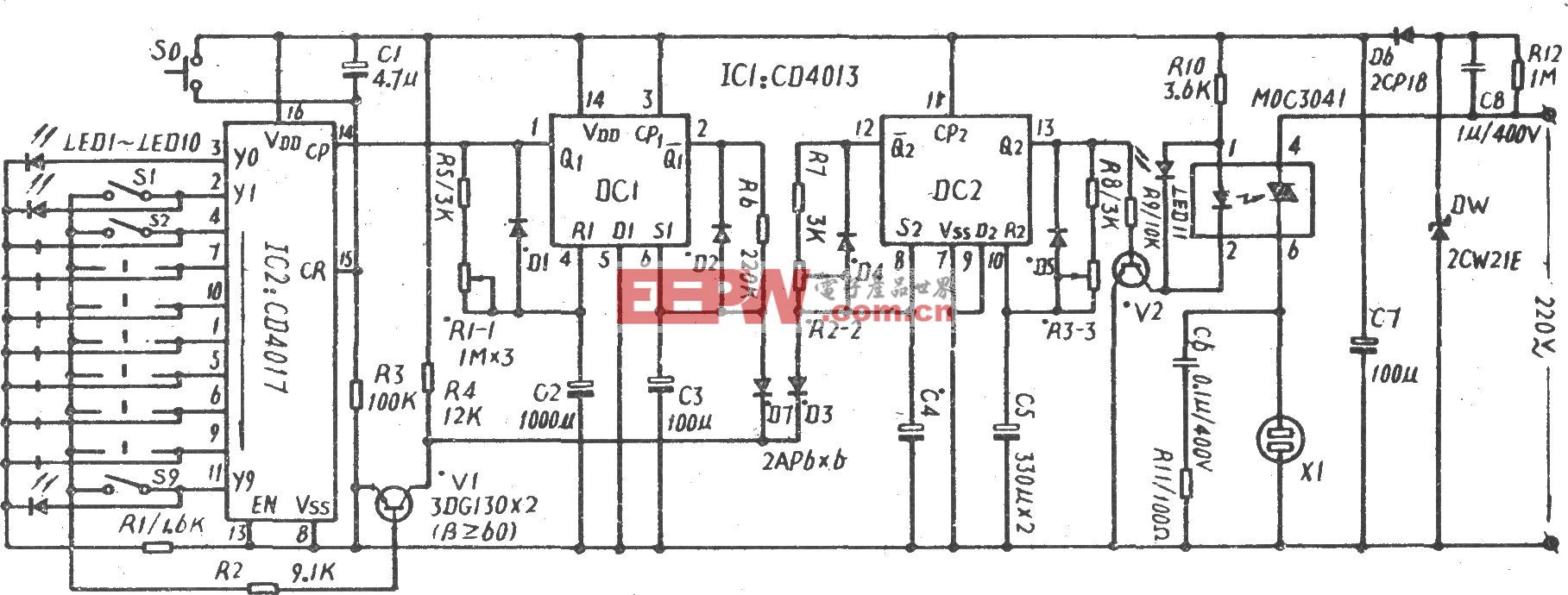

pascal三角形,即(a-b)n展開項系數(shù),是一個經(jīng)典的數(shù)學問題,然而它在通信、頻率補償、版圖布局布線優(yōu)化等 很多方面都有廣泛的應用。在一個小數(shù)分頻項目中,需要構建一個四級的pascal三角形來進行相位補償,如圖1所示,第二個累加器的溢出必須通過第一個微分控制分頻比,第三個累加器的溢出必須通過第二個微分控制分頻比,依此類推。第二個累加器使分頻比變?yōu)閚+1、n-1,第三個累加器將分頻比變?yōu)閚+1、n-2、n+1,第四個累加器的分頻比序列為n+1、n-3、n+3、n-1,正如圖2所示該序列構成一個pascal三角形,每行的總和為零。依照這個規(guī)律可以設計實現(xiàn)pascal 三角形運算的通用電路。

很多方面都有廣泛的應用。在一個小數(shù)分頻項目中,需要構建一個四級的pascal三角形來進行相位補償,如圖1所示,第二個累加器的溢出必須通過第一個微分控制分頻比,第三個累加器的溢出必須通過第二個微分控制分頻比,依此類推。第二個累加器使分頻比變?yōu)閚+1、n-1,第三個累加器將分頻比變?yōu)閚+1、n-2、n+1,第四個累加器的分頻比序列為n+1、n-3、n+3、n-1,正如圖2所示該序列構成一個pascal三角形,每行的總和為零。依照這個規(guī)律可以設計實現(xiàn)pascal 三角形運算的通用電路。

pascal三角形的數(shù)學描述

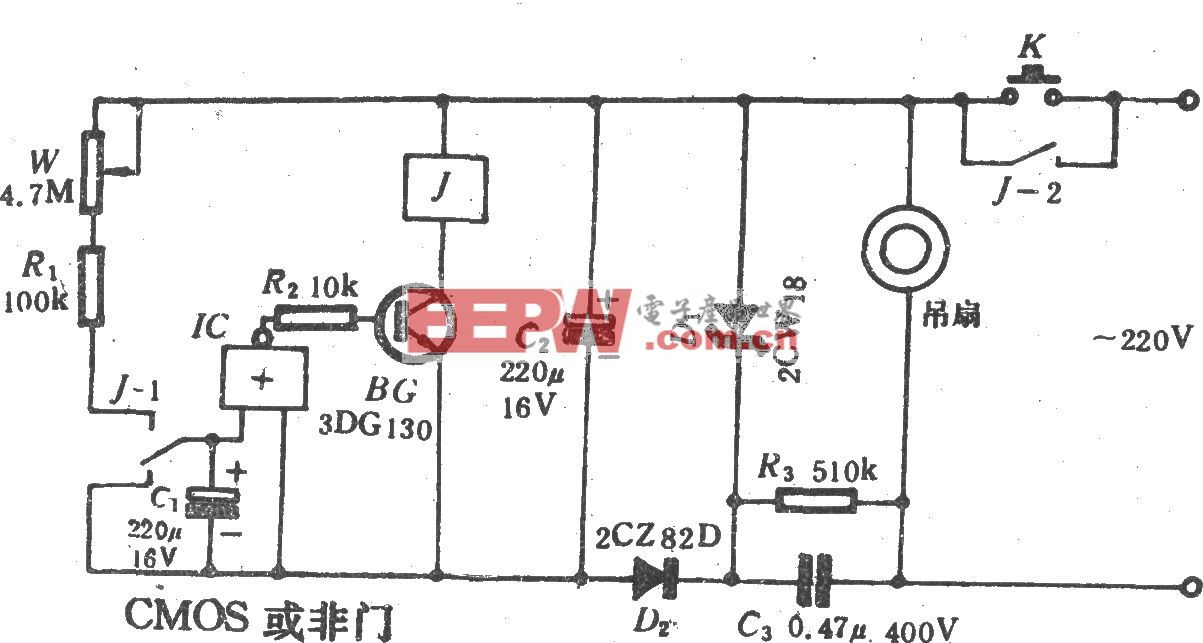

pascal三角形通常用三角形的方式來表示,如圖2所示,也可以用一個二維的下三角矩陣來描述,如圖3所示。

矩陣a[n,n]可以用下面的公式來描述。

a[i, j]=a[i, j-1]+(-1)a[i+1, j] (式1)

(a[n, 1]=0,a[n, 2]=a[n, 3]=...=a[n, n]=1)

i≥1,j≥2。

矩陣中第一列的0是為了方便電路實現(xiàn)而人為加上去的。將此二維矩陣表達式(即式1)變成含有時間的一維方程。

a[i]j=a[i]j-1+(-1)a[i+1]j (式2)

i,j均大于1,a[n]2 =a[n]3=...a[n]n=1。下標表示時間,a[n,1]=0表示剛開始整個電路的清零信號,其余第一

i,j均大于1,a[n]2 =a[n]3=...a[n]n=1。下標表示時間,a[n,1]=0表示剛開始整個電路的清零信號,其余第一 列的0表示對應pascal三角形的和為0,最后一行的1表示pascal三角形每一行對應的輸入端有輸入值1時,產(chǎn)生的立即數(shù)為1。

列的0表示對應pascal三角形的和為0,最后一行的1表示pascal三角形每一行對應的輸入端有輸入值1時,產(chǎn)生的立即數(shù)為1。

此外,式2具有疊加性,可以把pascal三角形中的一行加上其余任意一行或者幾行,實現(xiàn)任意時鐘周期的延時。

pascal三角形的基本電路

根據(jù)上面一維含時公式,先要構建補碼電路,然后是一個加法電路,最后是一個延時電路。

假設一個數(shù)組a[n:0]表示數(shù)的各位,a[0]為最低位,對各位取反,然后最低位加1,得到一個新的數(shù)組b[n:0],這個數(shù)組最低位為b[0],對應的邏輯關系是:

其余位按照這個規(guī)律依此類推,邏輯圖如圖4所示。

采用通用的全加器,邏輯表達式為:

示意圖參見圖5。其中ci為上一級的進位,a、b為本級輸入信號,s為全加和,co是本級進位。

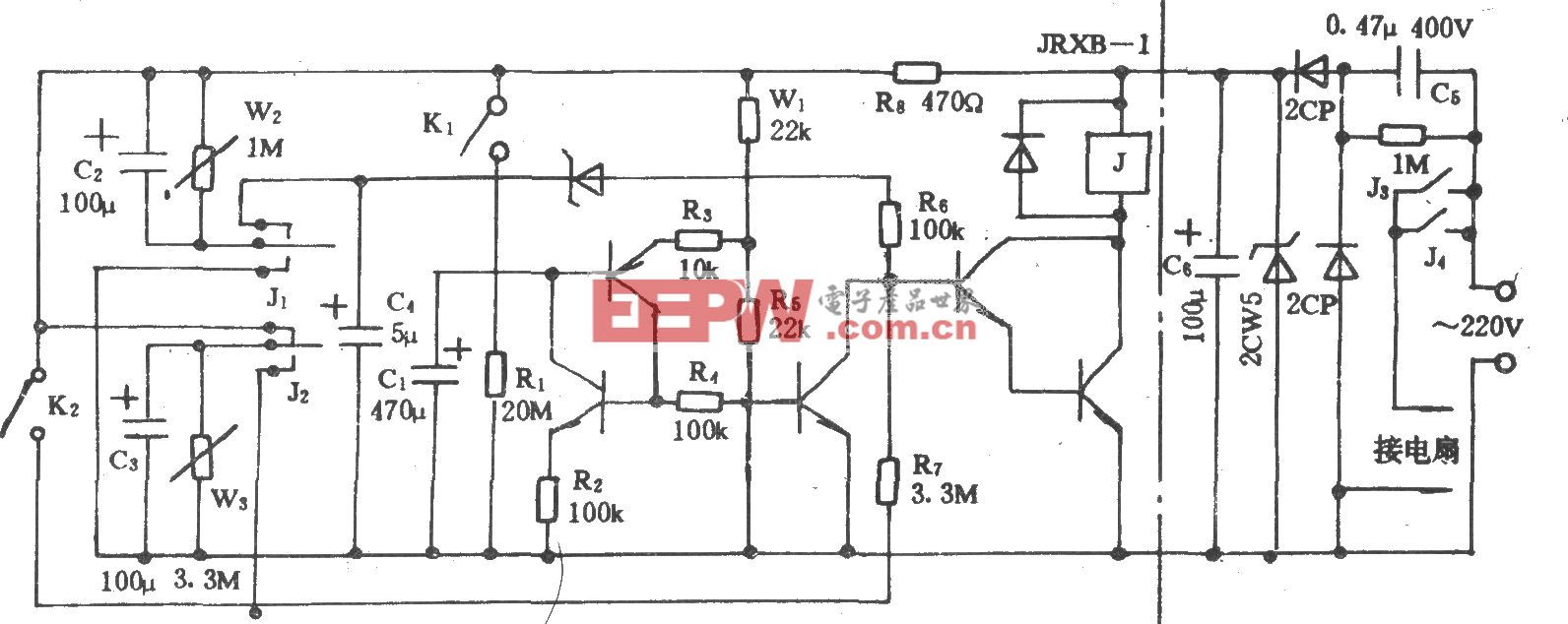

延時器采用帶清零的d觸發(fā)器來實現(xiàn),見圖6。clock為時鐘信號,clear為清零信號,d是數(shù)據(jù)輸入信號,q是原量輸出

。

電路設計

首先構建一個4級pascal三角形電路,其中clock是時鐘信號,in1、in2、in3、in4分別對應于pascal三角形的前4行,clear是清零信號。in1、in2、in3、in4輸入之前將觸發(fā)器清零,防止輸出不定態(tài)。d0、d1、d2、d3是從低到高的四位輸出,sign是符號位,這五位構成輸出。值得注意的是,in4經(jīng)過與自己直接相連的d觸發(fā)器產(chǎn)生的數(shù)只有一位,然而它的補碼需要4位,只好在高位加零,這樣補碼電路就可以簡化,圖7就是經(jīng)過簡化的電路圖。為了增加電路的直觀性,這里省略了電路中所有d觸發(fā)器的時鐘信號和清零信號,所有d觸發(fā)器的清零信號和時鐘信號分別連在一起。

圖7 pascal三角形實現(xiàn)電路

真值表

|

in4 |

in3 |

in2 |

in1 |

cp1 |

cp2 |

cp3 |

cp4 |

|

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

|

0 |

0 |

1 |

0 |

1 |

-1 |

0 |

0 |

|

0 |

0 |

1 |

1 |

2 |

-1 |

0 |

0 |

|

0 |

1 |

0 |

0 |

1 |

-2 |

1 |

0 |

|

0 |

1 |

0 |

1 |

2 |

-2 |

1 |

0 |

|

0 |

1 |

1 |

0 |

2 |

-3 |

1 |

0 |

|

1 |

0 |

0 |

0 |

1 |

-3 |

3 |

-1 |

|

1 |

0 |

0 |

1 |

2 |

-3 |

3 |

-1 |

|

1 |

0 |

1 |

0 |

2 |

-4 |

3 |

-1 |

|

1 |

0 |

1 |

1 |

3 |

-4 |

3 |

-1 |

|

1 |

1 |

0 |

0 |

2 |

-5 |

4 |

-1 |

|

1 |

1 |

0 |

1 |

3 |

-5 |

4 |

-1 |

|

1 |

1 |

1 |

0 |

3 |

-6 |

4 |

-1 |

|

1 |

1 |

1 |

1 |

4 |

-6 |

4 |

-1 |

電路的驗證與擴展

取in1、in2、in3、in4從0001到1111,并且給每組值以足夠的變化周期,可以得到下面的真值表。在viewlogic用xilinx公司的xc4000庫進行模擬,除了可以忽略的毛刺和初始時無關緊要的不定態(tài)之外,得到的波形圖與真值表完全一致,其中cp1、cp2、cp3、cp4分別對應于第1、2、3、4時鐘,周期波形圖如圖8所示。

圖8 波形圖

三級的電路得到驗證之后,根據(jù)同樣的原理,可以在四級的基礎上進行任意級的構建。

小結(jié)

本文給出了pascal三角形運算電路的設計思想與實現(xiàn)方法,以及在viewlogic下的驗證,并且還可以根據(jù)需要進行任意級的擴展。pascal三角形在版圖布局布線優(yōu)化等方面的具體應用可以參考有關文獻,在此不再贅述。

評論