基于VHDL的Petri網(wǎng)系統(tǒng)的FPGA實(shí)現(xiàn)

1 引言?

Petri網(wǎng)是一種系統(tǒng)的、數(shù)學(xué)的和圖形的描述和分析工具[1],隨著超大規(guī)模集成電路FPGA和CPLD的發(fā)展,Petri網(wǎng)的硬件實(shí)現(xiàn)成為可能,而基于Petri網(wǎng)的邏輯控制器的邏輯電路實(shí)現(xiàn)方法成為最近幾年的研究熱點(diǎn)[2]。在目前的Petri網(wǎng)硬件實(shí)現(xiàn)的研究中,主要給出了petri網(wǎng)C/E系統(tǒng)和P/T系統(tǒng)的幾種實(shí)現(xiàn)方法,但主要存在如下缺點(diǎn):1)使用基本門電路和觸發(fā)器用圖形法自底向上實(shí)現(xiàn)了Petri網(wǎng)基本元件庫(kù)所與變遷。這種設(shè)計(jì)方法的最大缺點(diǎn)是不易于任意修改邏輯電路設(shè)計(jì)。2)用VHDL語(yǔ)言實(shí)現(xiàn)了整體電路設(shè)計(jì)的軟件化,但未形成模塊化的Petri網(wǎng)元件。

VHDL語(yǔ)言由于其其強(qiáng)大的行為描述能力及與硬件行為無關(guān)的特性,被廣泛的用于數(shù)字系統(tǒng)設(shè)計(jì),實(shí)現(xiàn)了硬件電路設(shè)計(jì)的軟件化,成為實(shí)現(xiàn)Petri網(wǎng)邏輯控制器的有力的工具。用VHDL語(yǔ)言進(jìn)行數(shù)字電路設(shè)計(jì)的很大的優(yōu)勢(shì)是其自頂向下的設(shè)計(jì)方法,可以充分的實(shí)現(xiàn)電路的層次化設(shè)計(jì),從而很方便的修改頂層的控制器電路。本文分別用VHDL語(yǔ)言研究了幾種Petri網(wǎng)系統(tǒng)的硬件實(shí)現(xiàn),包括同步PN、時(shí)延PN,尤其是高級(jí)網(wǎng)系統(tǒng)有色PN。在當(dāng)前的研究中有色Petri網(wǎng)的硬件實(shí)現(xiàn)是一個(gè)難點(diǎn)。

2 同步Petri網(wǎng)的實(shí)現(xiàn)

2.1同步Petri網(wǎng)簡(jiǎn)介

定義1 [1]同步PN是一個(gè)三元組

R是一已標(biāo)識(shí)的PN

E是外界事件集

Sync是從R的變遷集到事件集的函數(shù)。

在同步PN中,每個(gè)變遷總是與一個(gè)事件相聯(lián)系,當(dāng)變遷是使能的,且與變遷聯(lián)系的事件發(fā)生時(shí),產(chǎn)生變遷的激發(fā)。

2.2同步Petri網(wǎng)的元件實(shí)現(xiàn)

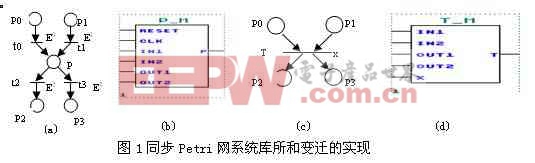

元件P_M實(shí)現(xiàn)了基本的同步Petri網(wǎng)系統(tǒng)(如圖1(a))中的庫(kù)所模塊,庫(kù)所P具有兩個(gè)輸入變遷和兩個(gè)輸出變遷,且每個(gè)變遷均與外部事件有關(guān)。當(dāng)庫(kù)所P中沒有托肯且?guī)焖鵓0或P1中有托肯時(shí),外部事件E發(fā)生,變遷t0或t1激發(fā),則托肯從庫(kù)所P0或P1移動(dòng)到庫(kù)所P;當(dāng)P中有托肯且?guī)焖鵓2或P3中沒有托肯時(shí),外部事件E發(fā)生,變遷t2或t3激發(fā),則托肯從庫(kù)所P移動(dòng)到庫(kù)所P2或P3;元件P_M(如圖1(b))是在EDA軟件Max+PlusⅡ中采用VHDL語(yǔ)言描述,經(jīng)過編譯、仿真后形成模塊并存放與元件庫(kù)中的。它有兩個(gè)輸入變遷in1,in2和兩個(gè)輸出變遷out1,out2,當(dāng)變遷激發(fā)時(shí),其值為邏輯1,否則為邏輯0;reset為復(fù)位信號(hào),用來設(shè)置庫(kù)所的初始狀態(tài)。clk為全局時(shí)鐘。P的值表示庫(kù)所中是否含有托肯,若含有托肯,取值為邏輯1,否則為邏輯0。

變遷元件T_M(如圖1(d)),具有兩個(gè)輸入庫(kù)所P0和P1,兩個(gè)輸出庫(kù)所P2和P3,且受外部事件x的控制,如圖1(c)所示,其激發(fā)規(guī)則是當(dāng)庫(kù)所P0和P1中有托肯,而庫(kù)所P2和P3中沒有托肯,且事件x發(fā)生時(shí),變遷激發(fā)。變遷元件T_M 輸入端in1,in2,out1,out2分別表示輸入庫(kù)所和輸出庫(kù)所中含有托肯的狀態(tài),若含有托肯,則取值為邏輯1,否則為邏輯0,x是外部事件。T表示變遷的激發(fā)狀態(tài),若可激發(fā)則取值為邏輯1。

用VHDL語(yǔ)言描述部分源程序如下:

architecture beh of t_m is

signal t0: std_logic;

begint=x and in1 and in2 and (not out1) and (not out2);end beh;

庫(kù)所元件P_M和變遷元件T_M均存放在Max+PlusⅡ中建立的元件庫(kù)中,是可以調(diào)用使用的。

評(píng)論