驗證FPGA設計:模擬,仿真,還是碰運氣?

一種可為大家接受的方法

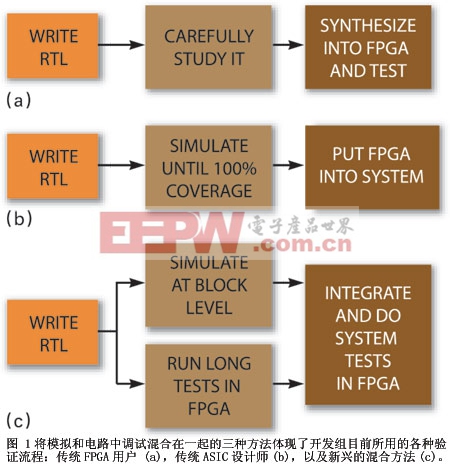

根據與FPGA廠商和用戶的討論,我們可以看到對模擬和仿真(圖1)混合驗證流程大家基本達成一致意見。這種流程首先對設計開始元件塊級的模擬——不是傳統上ASIC所用的那種窮舉式的力求完美的模擬,而更像是對實際情況進行檢查。其目標是驗證元件塊可用、引腳工作基本正確、在實驗環境中可滿足FPGA 的時序需要。

在此階段,很多開發組將某個版本的塊轉入FPGA并開始更為徹底的電路中測試。如果此電路塊(如視頻編解器)需要很長的高速數據流來驗證功能或是包括高速I/O功能,則該方法尤為常見。在其他情況下,繼續對塊進行模擬工作,直到所有問題都經過驗證,可以進行集成為止。

根據大家的一致意見,當開發組開始將塊集成時——建立試驗系統時——FPGA 才真正被更多人使用。這里,可能就是因為設計太大才無法進行快速模擬,或是對于已知可正常工作的塊,在FPGA上解決集成問題可能要比在模擬器上效率更高點。

但是,根據大家的意見,從模擬轉到仿真并不是單步的可逆步驟。正如軟件開發中并行進行模擬一樣,模擬工作在系統仿真期間也在繼續。多數開發組利用FPGA 仿真捕捉和隔離缺陷,然后將其送回模擬組診斷。在FPGA上做詳細診斷是非常痛苦的工作。

這里先總體敘述當前的情況,然后指出該方法的幾個嚴重缺點。首先,在兩個環境間來回傳送測試平臺數據很困難。似乎還沒有方法可以將創建測試的模擬指令自動映射到實施同一測試的 FPGA 結構。第二,各大 FPGA 廠商都可提供的嵌入式RISC核資源似乎遠沒有得到充分利用,它可以管理數據和控制測試,但是又是與模擬測試平臺分開的。理論上說,模擬組可以將其轉為嵌入式處理器核的C代碼,而不是轉為FPGA的RTL。第三,沒有簡單的途徑可以將FPGA 試驗中開發組收集的數據送回模擬平臺。最后,隨著模擬領域基于斷言的驗證工作不斷增多,FPGA 側急需一種類似的基于斷言的工具。

基于 FPGA的仿真系統銷售廠商對這些問題提出了應對措施(見附文 《解決覆蓋空隙的一些思路》),證明了這些問題是確實存在的。這里的例子有Eve公司的系統;模擬加速器,如GateRocket;以及“big-iron”(大型的)仿真盒,如Cadence的Palladium。至于這個基礎平臺會發展為FPGA驗證領域常見的那種專用板卡級仿真平臺,還是仍然會是昂貴的加速器和仿真系統的一種變形,我們尚無法知道。

評論